Epson Research and Development Page 19

Vancouver Design Center

Interfacing to the Philips MIPS PR31500/PR31700 Processor S1D13504

Issue Date: 01/02/02 X19A-G-005-08

5.4 Memory Mapping and Aliasing

When the PR31500/PR31700 accesses the PC Card slots without the ITE IT8368E, its

system memory is mapped as in Table 5-1:, “PR31500/PR31700 to Unbuffered PC Card

Slots System Address Mapping”.

Note

Bits CARD1IOEN and CARD2IOEN need to be set in the PR31500/PR31700 Memory

Configuration Register 3.

When the PR31500/PR31700 accesses the PC Card slots buffered through the ITE

IT8368E, bits CARD1IOEN and CARD2IOEN are ignored and the attribute/IO space of

the PR31500/PR31700 is divided into Attribute, IO and S1D13504 access. Table 5-2:,

“PR31500/PR31700 to PC Card Slots Address Remapping using the IT8368E” provides all

the details of the Attribute/IO address re-allocation by the IT8368E.

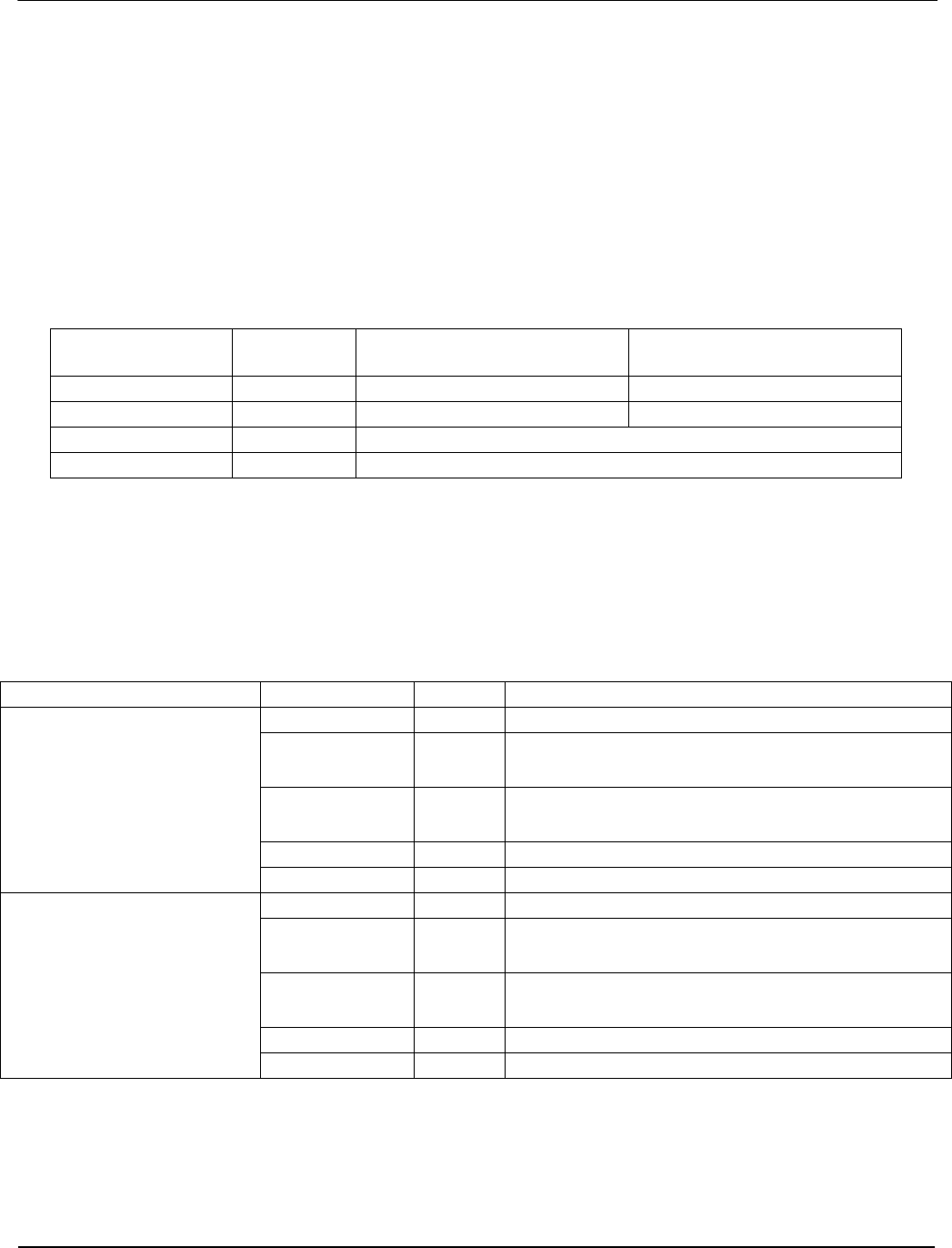

Table 5-1: PR31500/PR31700 to Unbuffered PC Card Slots System Address Mapping

TX3912 Address Size

Function

(CARDnIOEN=0)

Function

(CARDnIOEN=1)

0800 0000h 64M byte Card 1 Attribute Card 1 IO

0C00 0000h 64M byte Card 2 Attribute Card 2 IO

6400 0000h 64M byte Card 1 Memory

6400 0000h 64M byte Card 2 Memory

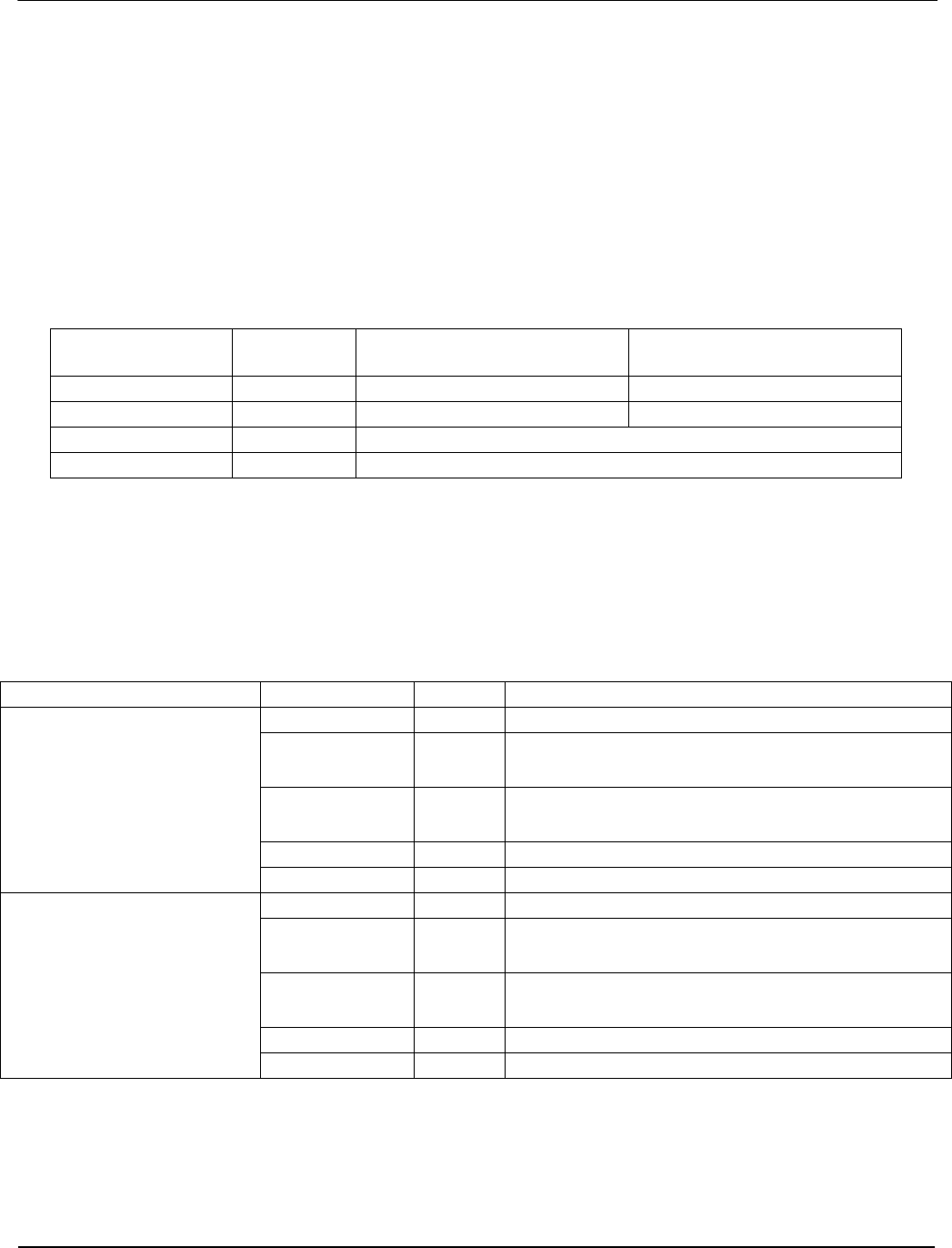

Table 5-2: PR31500/PR31700 to PC Card Slots Address Remapping using the IT8368E

IT8368E Uses PC Card Slot # Philips Address Size Function

1

0800 0000h 16M byte Card 1 IO

0900 0000h 8M byte

S1D13504 registers,

aliased 131,072 times at 64 byte intervals

0980 0000h 8M byte

S1D13504 display buffer,

aliased 4 times at 2Mb intervals

0A00 0000h 32M byte Card 1 Attribute

6400 0000h 64M byte Card 1 Memory

2

0C00 0000h 16M byte Card 2 IO

0D00 0000h 8M byte

S1D13504 registers,

aliased 131,072 times at 64 byte intervals

0D80 0000h 8M byte

S1D13504 display buffer,

aliased 4 times at 2Mb intervals

0E00 0000h 32M byte Card 2 Attribute

6800 0000h 64M byte Card 2 Memory