www.vxitech.com

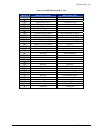

SM7100 Index 35

INDEX

A

A16 address space.............................................................23

A16 Base Address.............................................................21

A16 Offset Register..........................................................21

A16 Offset Register Address............................................21

A24 address space.............................................................21

A24 Base Address.............................................................21

A24/A32 Active................................................................23

A24/A32 Enable...............................................................23

A24/A32 Memory Offset..................................................24

A32 address space.............................................................21

A32 Base Address.............................................................21

Access LED Fail Bit.........................................................30

ACFAILN Enable Bit.......................................................29

address space ....................................................................13

Address Space...................................................................23

B

backplane jumpers............................................................11

BBM/MBB Bit .................................................................30

BBM/MBB Enable Bit .....................................................30

C

Cause/Status......................................................................24

command parsing..............................................................21

configuration registers......................................................29

cooling..............................................................................11

D

Data Bus ...........................................................................32

delay .................................................................................10

delay timer........................................................................30

Device Class.....................................................................23

direct register access...........................................................9

dynamic configuration......................................................23

E

Extended Memory Device................................................25

Extended Memory Space..................................................13

F

Firmware Version Number...............................................24

Front Panel Open Signal Operation Select Bit..................31

Front Panel Open Signal Polarity Bit................................31

Front Panel Open signal set by this module......................32

H

Handler IRQ Line.............................................................25

Hardware Revision Code..................................................32

I

IH ENA*..........................................................................25

Interrupt Mask.................................................................. 25

Interrupter IRQ Line ........................................................25

IR ENA* ..........................................................................25

IRQ line............................................................................25

L

logical address................................................ 11, 12, 13, 23

LSB (least significant bit) ..........................................12, 13

M

Major Hardware Version Number....................................24

Manufacturer's ID ............................................................23

memory space ..................................................................29

message-based.................................................................. 21

Minor Hardware Version Number.................................... 24

Model Code...................................................................... 23

MODID*.......................................................................... 23

Module Relay Address.....................................................33

MSB (most significant bit).........................................12, 13

O

Offset Register .................................................................21

offset value.......................................................................21

Openbus Out Enable Bit................................................... 30

P

polled fashion...................................................................24

power................................................................................11

R

register address.................................................................21

register-based device........................................................34

registers...................................................................... 21, 23

Relay Data Read Back Polarity Bit.................................. 29

Relay Register Address.................................................... 33

Relay Register Offset.......................................................33

Relay Reset Enable Bit ....................................................30

Relay Reset Select Bit......................................................30

Required Memory ............................................................23

Reset................................................................................. 23

S

scan list...............................................................................9

Sysfail Inhibit...................................................................23

T

triggers .............................................................................10