µ

PD30500, 30500A, 30500B

29

Data Sheet U12031EJ3V0DS00

DIFFERENCES BETWEEN THE VR5000 AND VR4310

TM

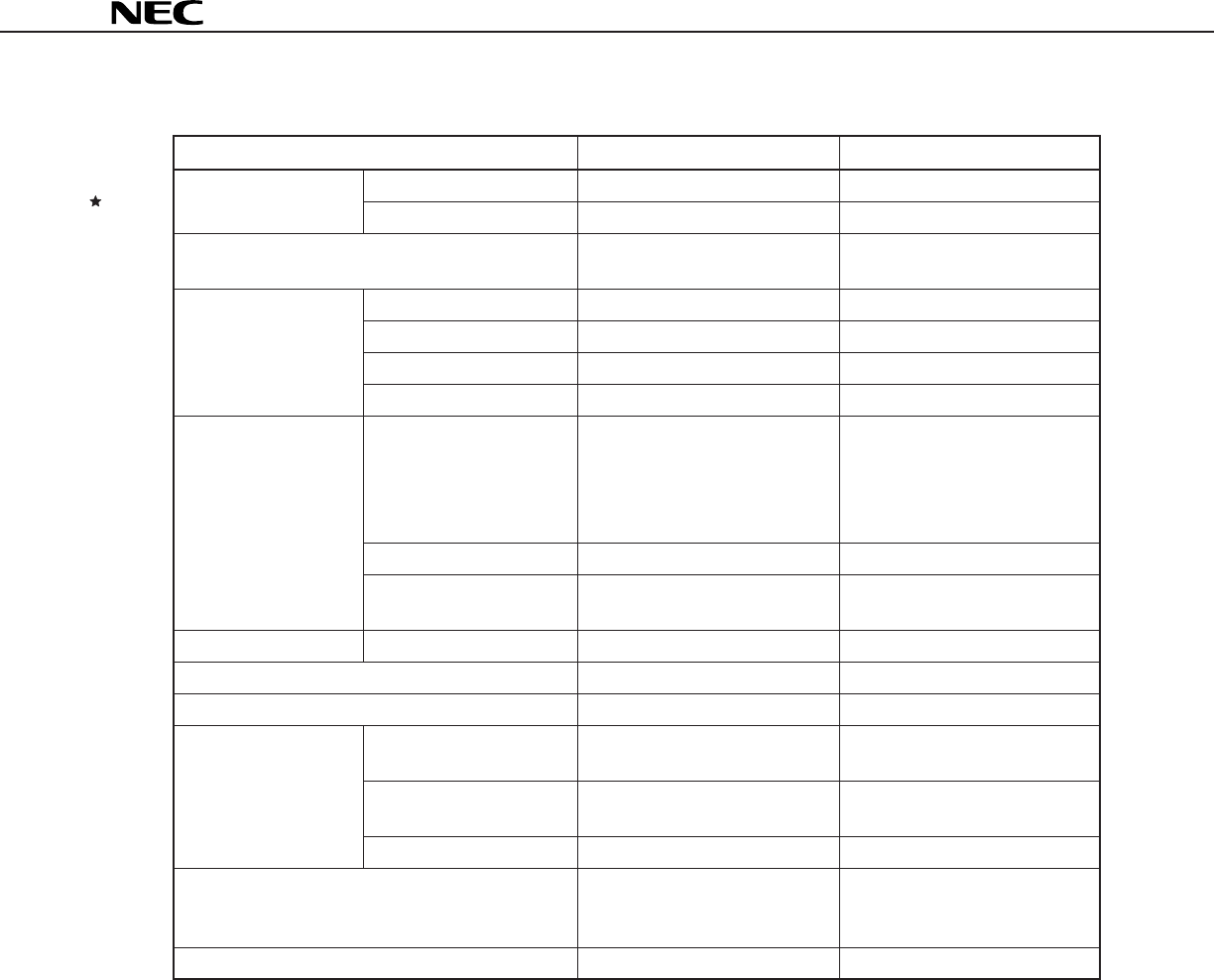

Item VR5000 VR4310

Operating frequency Internal 200 MHz MAX. 167 MHz MAX.

External 100 MHz MAX. 83.3 MHz MAX.

Pipeline 2-way super scalar 5-stage 5-stage pipeline

pipeline

Cache Primary instruction cache 32K bytes 16K bytes

Primary data cache 32K bytes 8K bytes

Secondary cache interface Provided None

Data protection Byte parity None

System bus Write data transfer rate 9 types (DDDD/DD×DD×/ 2 types (D/D××)

DD××DD××/D×D×D×D×/

DD×××DD×××/DD××××DD××××/

D××D××D××D××/

DD××××××DD××××××/D×××D×××)

Initialization pin at reset ModeIn (dedicated serial pin) DivMode (0:2)

Status after last data write Access ends Last data retained when transfer

rate is set

Integer operation unit Corresponding instruction MIPS I, II, III, IV instruction sets MIPS I, II, III instruction sets

JTAG interface None Provided

SyncOut-SyncIn bus None Provided

Clock interface Multiplication ratio of input 2, 3, 4, 5, 6, 7, 8 1.5, 2, 2.5, 3, 4, 5, 6

to internal

Division ratio of internal to 2, 3, 4, 5, 6, 7, 8 1.5, 2, 2.5, 3, 4, 5, 6

bus

Clock output None TClock

Low-power mode Pipline does not operate. Pipeline/system bus operates

at power of 1/4 of normal

operation.

PRId register Imp = 0×23 Imp = 0×0B