58

PRELIMINARY

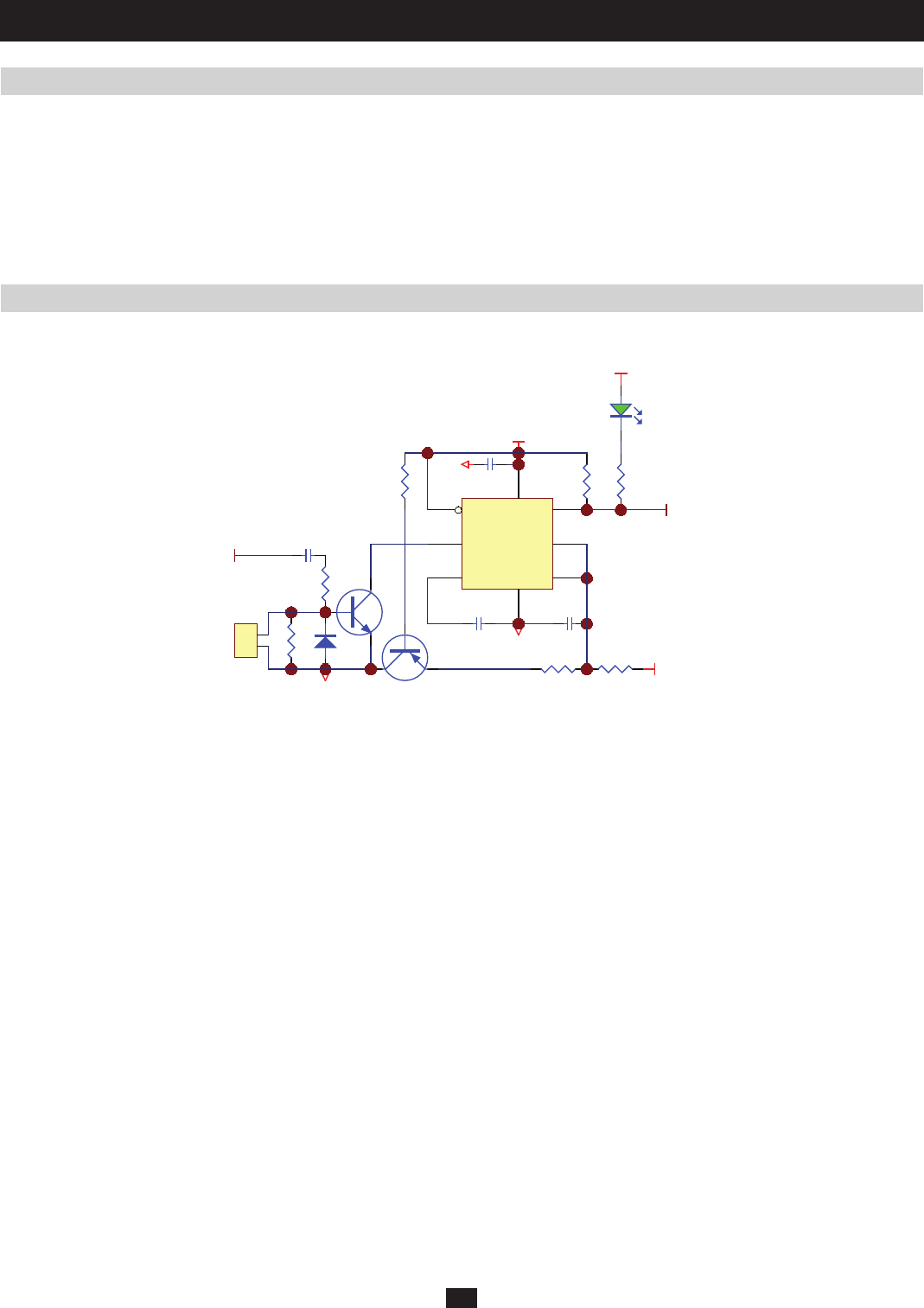

(a) The bypass SCR driver signal “BYPSTS1” is controlled by MCU or “TOBYP_J” according to the signal “CENTRAL_OK.”

(b) “CENTRAL_OK” is the output of MCU watchdog. If MCU is operating normally, “CENTRAL_OK” will be high and the bypass SCR driver

signal will be controlled by “BYPSTS” (1) (high active). If MCU is not operating normally, “CENTRAL_OK” will be low and the bypass SCR

driver signal will be controlled by “TOBYP_J” (high active).

(c) UM9 is a 45 kHz self-oscillator that can provide pulse signal for driver bypass SCR.

(d) The “TOBYP_J” signal is limited by “#TOBYP_I.”

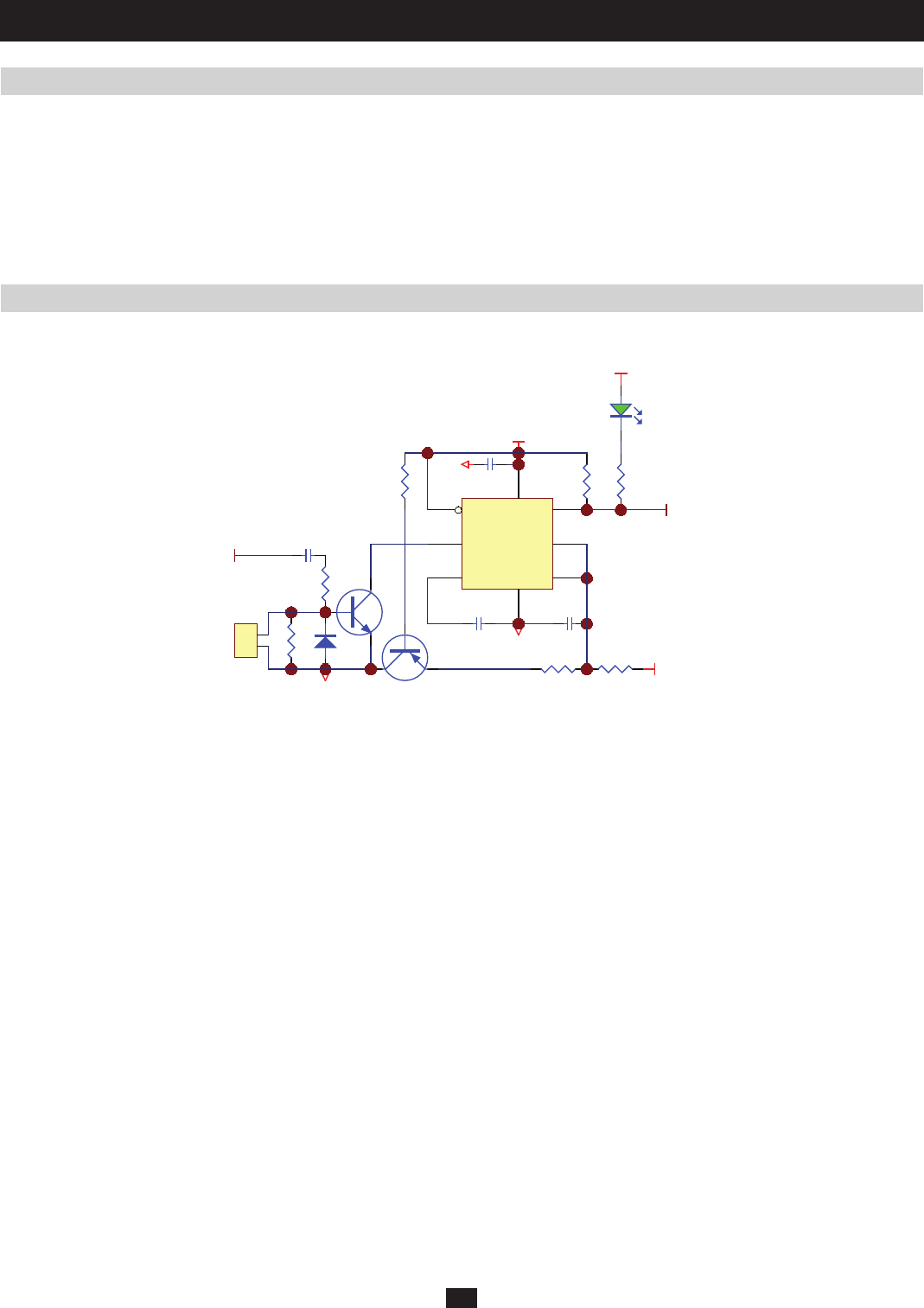

(a) SYS_RDY (4) will send out a pulse to reset CM46. CM46 will then be recharged by 5V through RM88. “CENTRAL_OK” will maintain a high

level. If SYS_RDY (4) does not send out a pulse during a specifi c period (for example, during an MCU crash), then “CENTRAL_OK” will be

low.

(b) Test JUMP (CNM2): If CNM2 is shorted, then “CENTRAL_OK” will be low. If CNM2 is opened, “CENTRAL_OK” will stay high during

normal operation.

2 Theory of Operation (continued)

2.9 Bypass SCR Driver (continued)

2.10 Watchdog for System MCU

Located at NH-SYS-M board (System MCU and Control Circuit)

TRIG

2

Q

3

R

4

CVol t

5

THR

6

DIS

7

VCC

8

GND

1

UM3

TLC555C

RM72

G1

5VS

CM3 6

G1

CM4 5

RM8 8

5VS

QM5

RM7 1

QM3

DM24

RM8 1

CM3 9

G1

CM4 6

RM8 9

1

2

CNM2

2.5X2P

RM8 6

(70)

(4)

CE NT RAL _ O

RM1

LEDM1

LED(GRN)

5VS

SYS_ RDY