30

www.amctechcorp.com

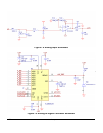

Pins 1-5 on the DIMM socket control the Ethernet port on the NETdimm

TM

. Pins 6-8 control the In-

Circuit Emulator. Pins 9-13 control the UART port. Pins 14-20 control the LCD. Pins 21-22 control the

USB port. Pins 23-29 control the SPI. Finally, pins 30-84 control the PCI bus.

PCI

The PCI interface on the dimmPCI

TM

CPU module is constructed around a Cypress

CY7C09449PV-AC bus controller. This controller is an integrated PCI bridge, master/slave direct

memory access controller (DMAC), message transport unit (I2O) and contains 32kbytes of dual

ported memory (DPRAM).

The local bus (LB) may access four areas with the CY7C09449; an 8K direct access window into

any of the PCI address spaces (memory, I/O or configuration space), the 32kbyte DPRAM, the

I2O FIFOs, and the control registers. Any PCI master may access only the last three areas;

further, PCI masters may not access the local bus (neither the CY7C09449 nor the 68VZ328

support this).

The DPRAM may be used as either source or destination for PCI DMA transfers, which may be

initiated locally (as a master) or by another host (as a target).

The CY7C09449 is attached to a 32-bit synchronous local bus. An Altera EPM7032AE FPGA is

required to attach the CY7C09449 to the 16bit asynchronous bus of the Dragonball VZ.

When the dimmPCI

TM

CPU module is used in the system slot (slot 1), SYSEN line is pulled low;

the 7032AE performs various PCI central resource functions including RESET generation,

CLOCK generation and bus REQUEST and GRANT arbitration.

PCI BIOS

The PCI BIOS establishes a software interface between the PCI device drivers and the

CY7C09449 hardware. When the dimmPCI

TM

CPU module is in the system slot, the PCI BIOS also

performs the scanning and initialization of devices attached to the PCI bus. Base memory and I/

O addresses are assigned, as are the shared PCI interrupt request lines.

Expansion ROMs (used by PC compatible video cards and the like) are not supported, as the

Dragonball does not support the x86 code.

The PCI BIOS includes the standard ‘pcibios_read/write_config_byte/word/dword’ functions.

All PCI spaces are defined to be small endian. The Dragonball, which is large endian, has been

attached to the C7C09449 such that word accesses do not require byte swapping; byte accesses

require toggling the least significant address bit. This is made transparent by the PCI BIOS and