78 CY4672 Reference Design Guide, Document # 001-16968 Revision **

Bridge

5.3 Firmware Architecture

There are two architectural views of the bridge. The first is a microcontroller configuration view of

User Modules inside the controller. This architecture and configuration is best viewed in the PSoC

Designer application when the project is loaded. The second view is a logical organization of the

source code modules that make up the bridge application code and other support modules.

The next two sections describe both architectures with emphasis on top-level organization and over-

all module operation. To obtain more detailed descriptions of variables and functions, reference the

source code.

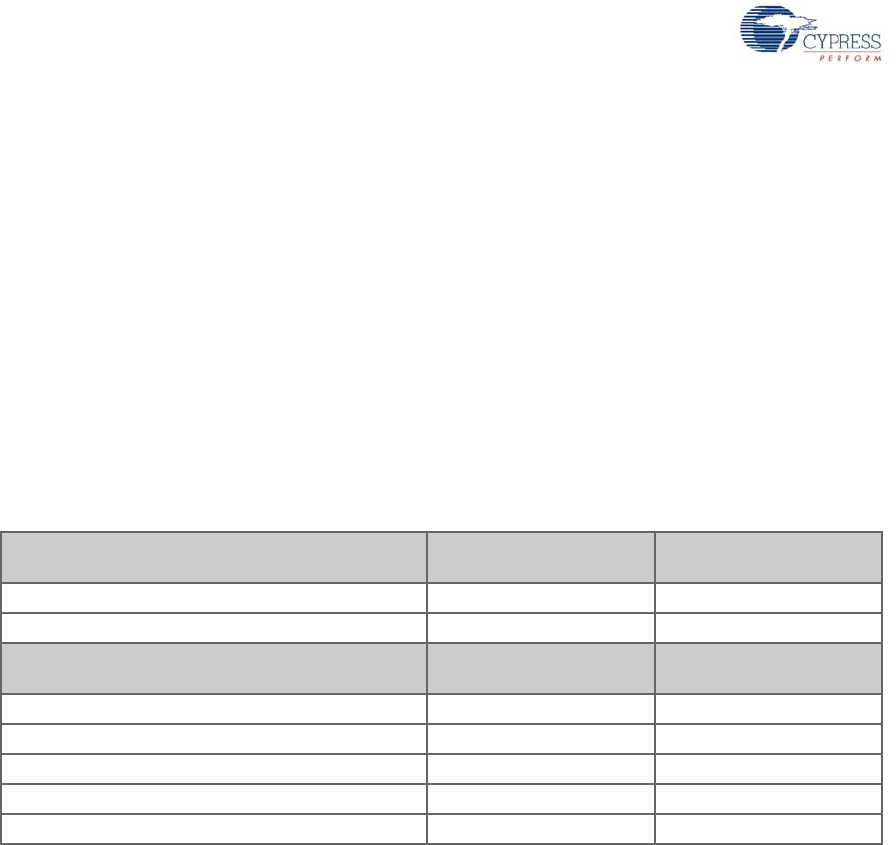

5.3.1 ROM/RAM Usage

The following table shows the ROM/RAM usage. The top part exhibits the total ROM/RAM usage for

basic functions, which disables all the build options below. The bottom part exhibits the ROM/RAM

usage for individual build options.

*The ENCRYPT_TEA option needs 64 bytes of extra ROM space to store the non-volatile session

key.

5.3.2 PRoC LP Device Configuration

The PRoC LP Programmable Radio on Chip is configured using the Device Editor in PSoC

Designer. The bridge uses the SPI Master, USB Device, and the 1 Millisecond Interval Timer User

Modules. The SPI Master User Module is used by firmware to communicate with the LP radio mod-

ule. The USB Device User Module allows the bridge to operate as a low-speed USB device. The 1

Millisecond Interval Timer User Module is used for timing. Following is a screen shot of the Device

Editor showing the User Module mapping. Further description of resources and User Modules follow

the diagram.

Table 5-1. ROM/RAM Usage

Total ROM (Bytes) Total RAM (Bytes)

Basic Functions 7251 170

Build Option ROM Usage (Bytes) RAM Usage (Bytes)

ENCRYPT_DATA TEA* 815 29

ENCRYPT_DATA AES 990 35

MFG_TEST_CODE 541 0

MFG_TX_MODES 651 2

BACK_CHANNEL_SUPPORT 147 1

[+] Feedback