Chapter 3 Programming Your Universal Counter for Remote Operation

Status Reporting

3-22 Programming Guide

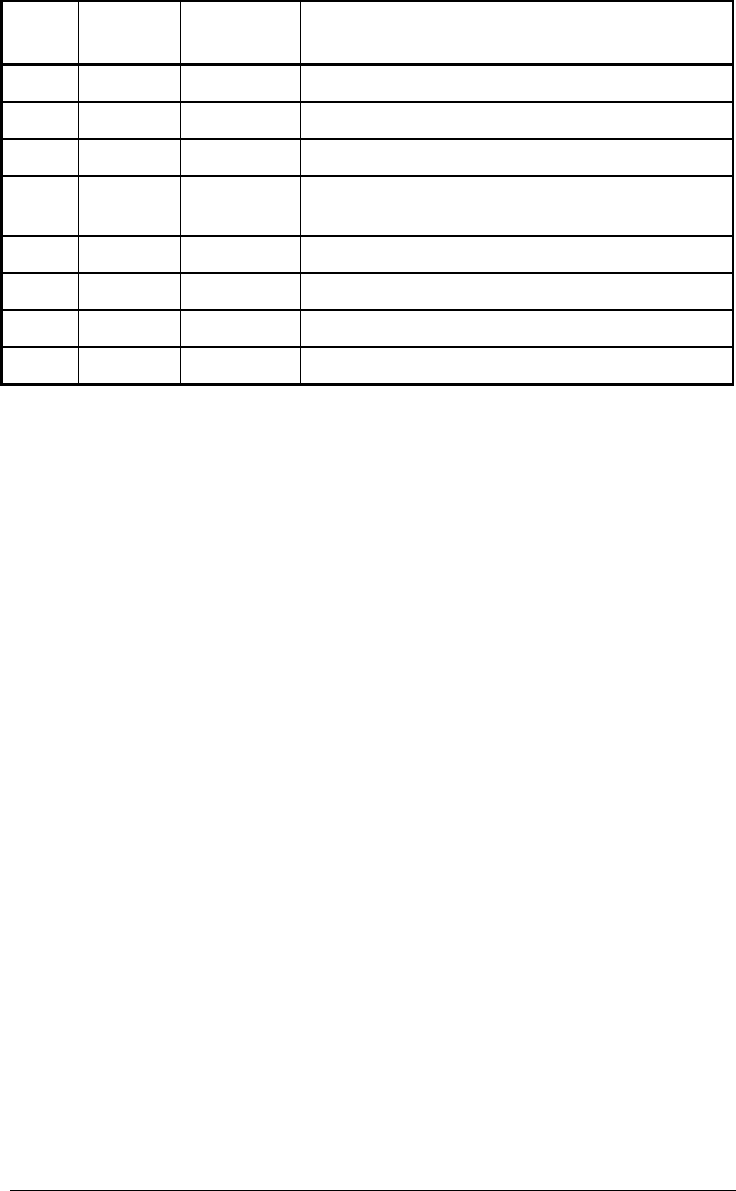

Table 3-4. Status Byte Register

BIT WEIGH

T

SYMBOL DESCRIPTION

0 Not used

1 Not used

2 Not used

3 8 QSB

Questionable Data/Signal Status Register

Summary Bit

4 16 MAV Message Available Summary Bit

5 32 ESB Standard Event Status Register Summary Bit

6 64 RQS/MSS Request Service/Master Status Summary Bit

7 128 OSB Operation Status Register Summary Bit

A detailed description of each bit in the Status Byte Register follows:

• Bits 0–2 are not used.

• Bit 3 (QSB) summarizes the Questionable Data/Signal Status Event

Register.

This bit indicates whether or not one or more of the enabled Questionable

Data/Signal events have occurred since the last reading or clearing of the

Questionable Data/Signal Status Event Register.

This bit is set TRUE (one) when an enabled event in the Questionable

Data/Signal Status Event Register is set TRUE. Conversely, this bit is set

FALSE (zero) when no enabled events are set TRUE.

• Bit 4 (MAV) summarizes the Output Queue.

This bit indicates whether or not the Output Queue is empty.

This bit is set TRUE (one) when the Counter is ready to accept a request

by the external computer to output data bytes; that is, the Output Queue is

not empty. This bit is set FALSE (zero) when the Output Queue is empty.