I

2

C Bus Characteristics

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

7-18 Freescale Semiconductor

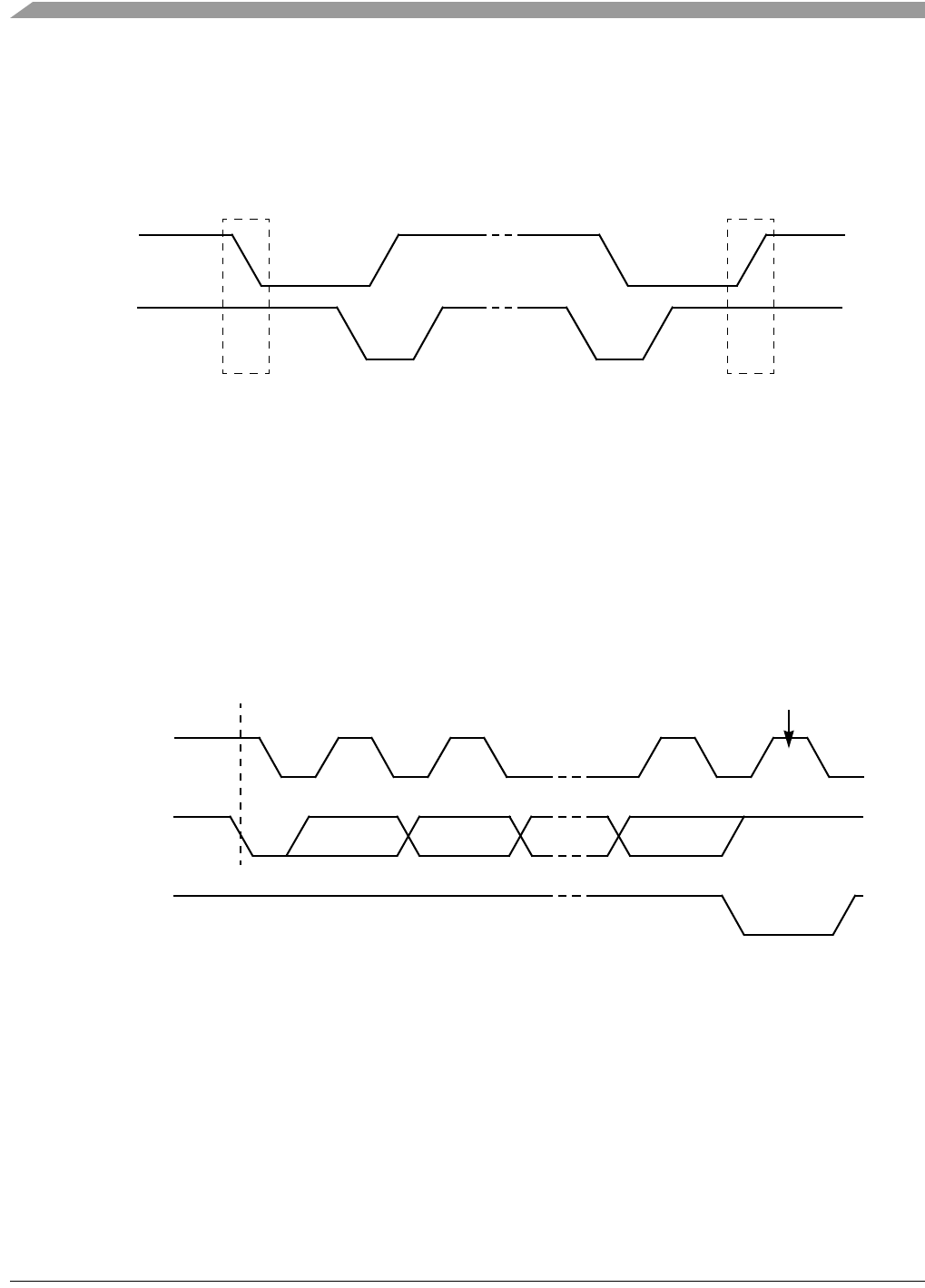

• Stop data transfer—The stop event is defined as a change in the state of the data line, from low

to high, while the clock is high (see Figure 7-8).

• Data valid—The state of the data line represents valid data when, after a Start event, the data line

is stable for the duration of the high period of the clock signal. The data on the line may be changed

during the low period of the clock signal. There is one clock pulse per bit of data.

Figure 7-8 I

2

C Start and Stop Events

Each 8-bit word is followed by one acknowledge bit. This acknowledge bit is a high level put on the bus

by the transmitter when the master device generates an extra acknowledge-related clock pulse. A slave

receiver that is addressed is obliged to generate an acknowledge after the reception of each byte. Also, a

master receiver must generate an acknowledge after the reception of each byte that has been clocked out

of the slave transmitter. The device that acknowledges has to pull down the SDA line during the

acknowledge clock pulse in such a way that the SDA line is stable low during the high period of the

acknowledge-related clock pulse (see Figure 7-9).

Figure 7-9 Acknowledgment on the I

2

C Bus

By definition, a device that generates a signal is called a “transmitter,” and the device that receives the

signal is called a “receiver.” The device that controls the signal is called the “master” and the devices that

are controlled by the master are called “slaves”. A master receiver must signal an end-of-data to the slave

transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave device.

In this case the transmitter must leave the data line high to enable the master generation of the stop event.

Handshaking may also be accomplished by use of the clock synchronizing mechanism. Slave devices can

hold the SCL line low, after receiving and acknowledging a byte, to force the master into a wait state until

S P

Start Event Stop Event

SDA

SCL

AA0423

Start

Event

Clock Pulse For

Acknowledgment

S

12 89

SCL From

Master Device

Data Output

by Transmitter

Data Output

by Receiver

AA0424