Intel

®

IXP400 Software

Access-Layer Components: Feature Control (IxFeatureCtrl) API

April 2005 IXP400 Software Version 2.0 Programmer’s Guide

184 Document Number: 252539, Revision: 007

stepping. For the IXP42X product line, this register is used to determine the maximum core

clock speed.

Note: CP15, Register 0 is read-only.

• EXP_UNIT_FUSE_RESET register in the Expansion Bus Controller - A software copy of this

register, called the

Feature Control Register, can be created and manipulated by this software

component.

The Feature Control Register is a structure which contains information on which components

are physically available on the processor. The detectable capabilities include the existence of

key coprocessors or peripherals (PCI controller, AES coprocessor, NPEs, etc.). The

ixFeatureCtrlHwCapabilityRead( ) function utilizes this register for detecting host processor

capabilities.

Note: The only way to detect the core frequency on the IXP46X product line is to use the

ixFeatureCtrlHwCapabilityRead( ) and check bits 22 and 23.

12.3.1 Using the Product ID-Related Functions

The functions ixFeatureCtrlDeviceRead ( ) and ixFeatureCtrlProductIdRead( ) return values

based upon the CP15 register discussed above. ixFeatureCtrlProductIdRead() returns the entire 32-

bit value, as documented below. ixFeatureCtrlDeviceRead() only returns an indication of the

processor product line; the IXP46X product line or IXP42X product line.

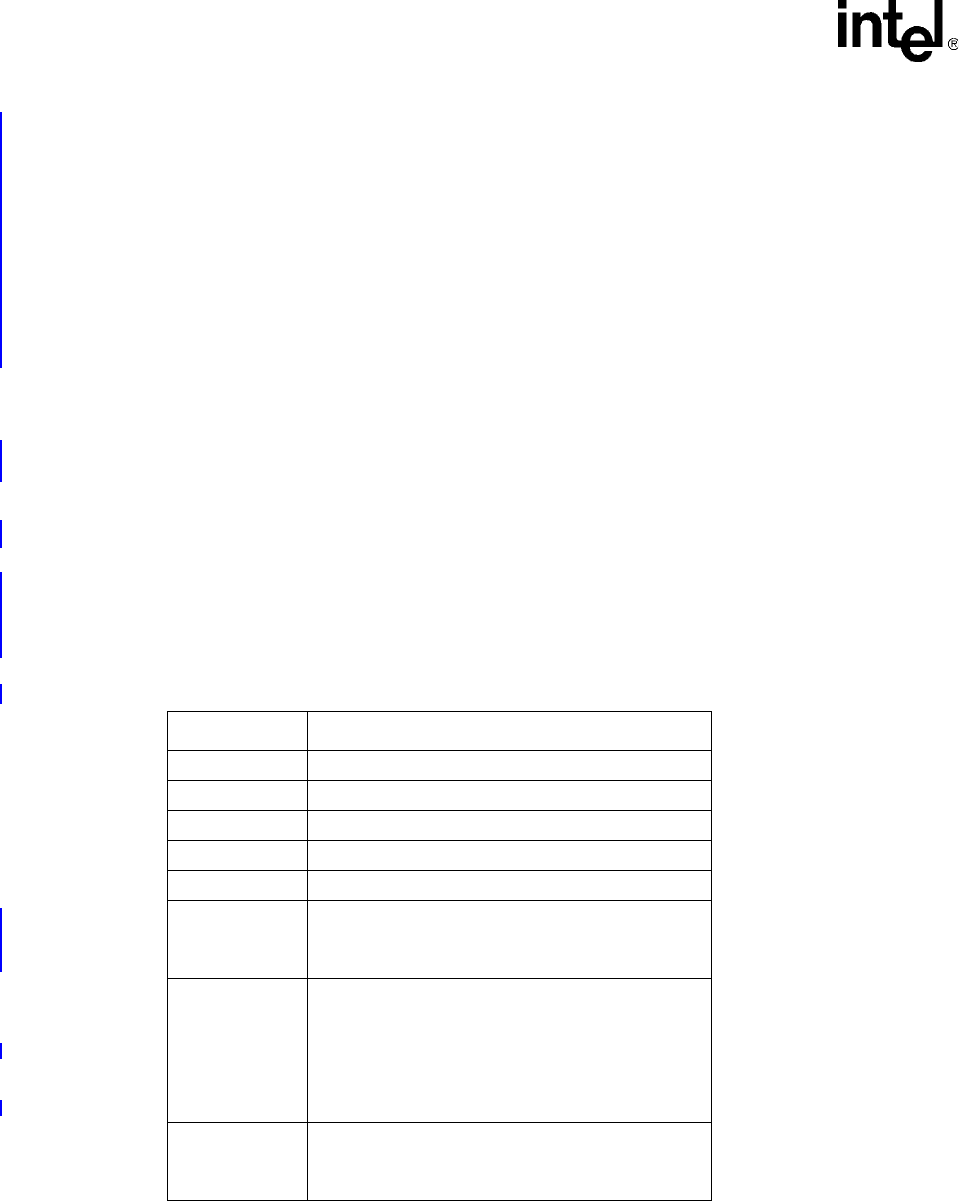

Table 36. Product ID Values

Bits Description

31:28 Reserved. Value: 0x6

27:24 Reserved. Value: 0x9

23:20 Reserved. Value: 0x0

19:16 Reserved. Value: 0x5

15:12 Reserved. Value: 0x4

11:9

Device ID.

IXP42X - 0x0

IXP46X - 0x1

8:4

Maximum Achievable Intel XScale

®

Core Frequency

for the IXP42X product line only.

533 MHz — 0x1C

400 MHz — 0x1D

266 Mhz — 0x1F

For the IXP46X product line, the value will be 0x00

.

3:0

Si Stepping ID.

A-step — 0x0

B-step — 0x1