Intel

®

IXP400 Software

Access-Layer Components: Feature Control (IxFeatureCtrl) API

Programmer’s Guide IXP400 Software Version 2.0 April 2005

Document Number: 252539, Revision: 007 185

12.3.2 Using the Feature Control Register Functions

The ixFeatureCtrlHwCapabilityRead( ) function utilizes the EXP_UNIT_FUSE_RESET register

for detecting host processor capabilities. A software structure for storing the changeable values for

each option is provided, and accessed using the ixFeatureCtrlRead ( ).

The mechanism which can simulate the disabling of components of the processor is a software

array,

IxFeatureCtrlReg, that can be written with the ixFeatureCtrlWrite() function and read by

ixFeatureCtrlRead().

The IxFeatureCtrl component does not actually write values to the EXP_UNIT_FUSE_RESET

register.

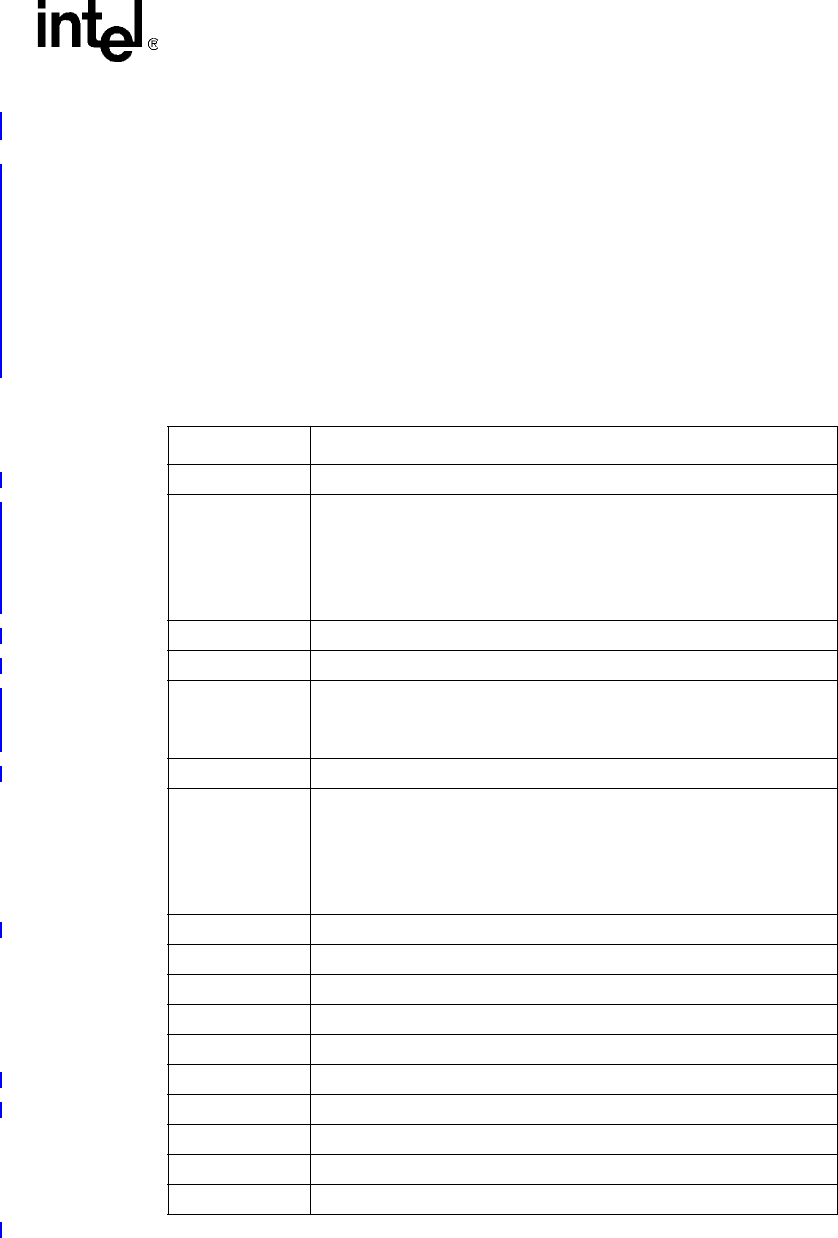

Table 37. Feature Control Register Values (Sheet 1 of 2)

Bits Description

31:24 (Reserved)

23:22

Processor frequency (IXP46X product line only):

0x0 - 533 MHz

0x1 - 667 MHz

0x2 - 400 MHz

0x3 - 266 MHz

21

†

RSA Crypto Block coprocessor (IXP46X product line only)

20

†

NPE B Ethernet coprocessor 1-3 (IXP46X product line only)

19

IXP46X product line only

0 = NPE A Ethernet is enabled if Utopia bit is 1.

1 = NPE A Ethernet is disabled.

18

†

USB Host Coprocessor (IXP46X product line only)

17:16

UTOPIA PHY Limits.

32 PHYs: 0x0

16 PHYs: 0x1

8 PHYs: 0x2

4 PHYs: 0x3

15

†

ECC and 1588 Unit (IXP46X product line only)

14

†

PCI Controller

13

†

NPE C

12

†

NPE B

11

†

NPE A

10

†

Ethernet 1 Coprocessor (on NPE C)

9

†

Ethernet 0 Coprocessor (on NPE B)

8

†

UTOPIA Coprocessor

7

†

HSS Coprocessor

6

†

AAL Coprocessor

† For bit 0 through 15, 18, 20-21 the following values apply:

• 0x0 — The hardware component exists and is not software disabled.

• 0x1 — The hardware component does not exist, or has been software disabled.