Intel

®

IXP400 Software

Access-Layer Components: Parity Error Notifier (IxParityENAcc) API

Programmer’s Guide IXP400 Software Version 2.0 April 2005

Document Number: 252539, Revision: 007 241

16.4.2 Summary Parity Error Recovery Scenario

IxParityENAcc does not perform parity error recovery tasks. This should be done by the client

application.

When notified of any failure, the client application should identify the affected components by

calling a function to fetch the Parity Error Context and decide on the appropriate course of action

considering the impact on its functionality. For example:

• Reset the whole system immediately.

• Graceful shutdown of the system after taking the necessary actions to minimize the impact

(informing the peers that it is about to shut down, tear down communication channels, etc.)

• Other means, depending on the application and data integrity requirements.

The internal memories of NPEs, the Switching Coprocessor and AHB Queue Manager do not

provide for an error correction facility. The DDR SDRAM controller implements a single-bit error

correction mechanism that requires the Intel XScale core to read and write the faulty memory

location.

When the DDR controller notifies the Intel XScale core about an error, error handling may vary

slightly, depending on the operating system and Intel XScale core MMU configurations. The user

application should provide a scrub routine for single-bit parity errors. This routine will be

responsible for disabling interrupts, memory mapping, flushing of cache lines before reading the

faulty word and after writing back the correct word onto it and finally enabling the interrupts.

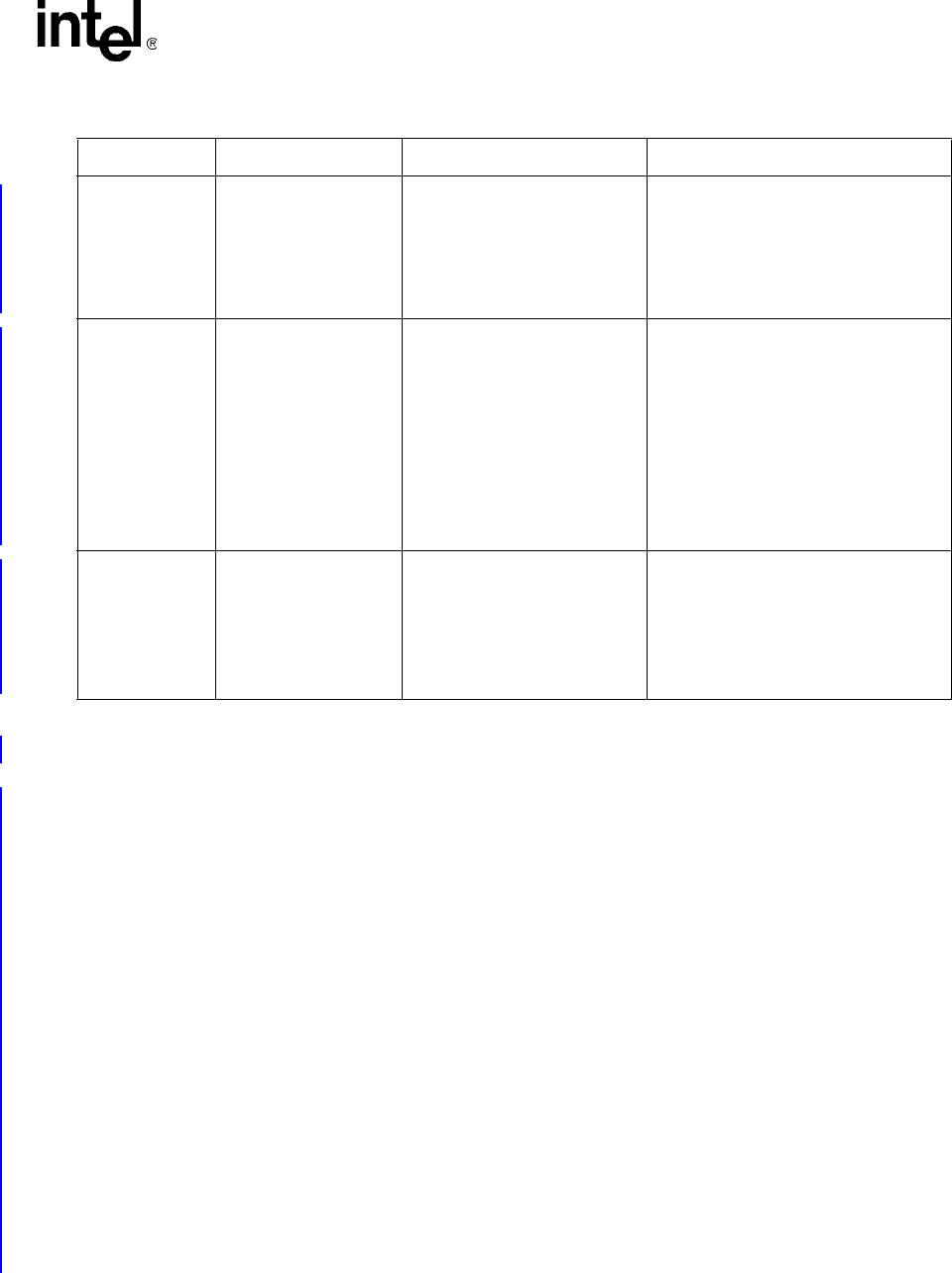

Int60 AQM Client Callback

Interrupt will be masked off at the

interrupt controller so that it will not

trigger continuously.

Client application has to take appropriate

action and needs to reconfigure the parity

error detection subsequently so that it is

notified of the interrupts.

Int61 MCU

Client Callback of Data Abort

Handler

Parity interrupt condition is cleared at the

SDRAM MCU for the following:

• Single-bit

•Multi-bit

• Overflow condition, i.e., more than

two parity conditions occurred.

Note that single-parity errors do not result

in data abort and not all data aborts are

caused by multi-bit parity error. Refer to

“Parity Error Notification Detailed

Scenarios” on page 242.

Int62 EXP Client Callback

Parity interrupt condition is cleared at the

Expansion Bus Controller for the

following:

• External master initiated Inbound

write

• Internal master (IXP46X network

processors) initiated Outbound read.

Table 47. Parity Error Interrupt Deassertion Conditions (Sheet 2 of 2)

Interrupt Bit Source API Invoked by... Action Taken During Interrupt Clear