Intel

®

IXP400 Software

Endianness in Intel

®

IXP400 Software

April 2005 IXP400 Software Version 2.0 Programmer’s Guide

358 Document Number: 252539, Revision: 007

The IP stack typically has an alignment restriction on the IP packet. The start of the IP packet must

be word-aligned, that is, the ver/hlen field shown above must start on a 32-bit boundary. There are

14 bytes of Ethernet frame data preceding the IP header. Thus ix_data pointers typically need to be

half-word-aligned (16 bits). This is the case that is discussed in this chapter, and in the Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor:

Understanding Big Endian and Little Endian Modes Application Note.

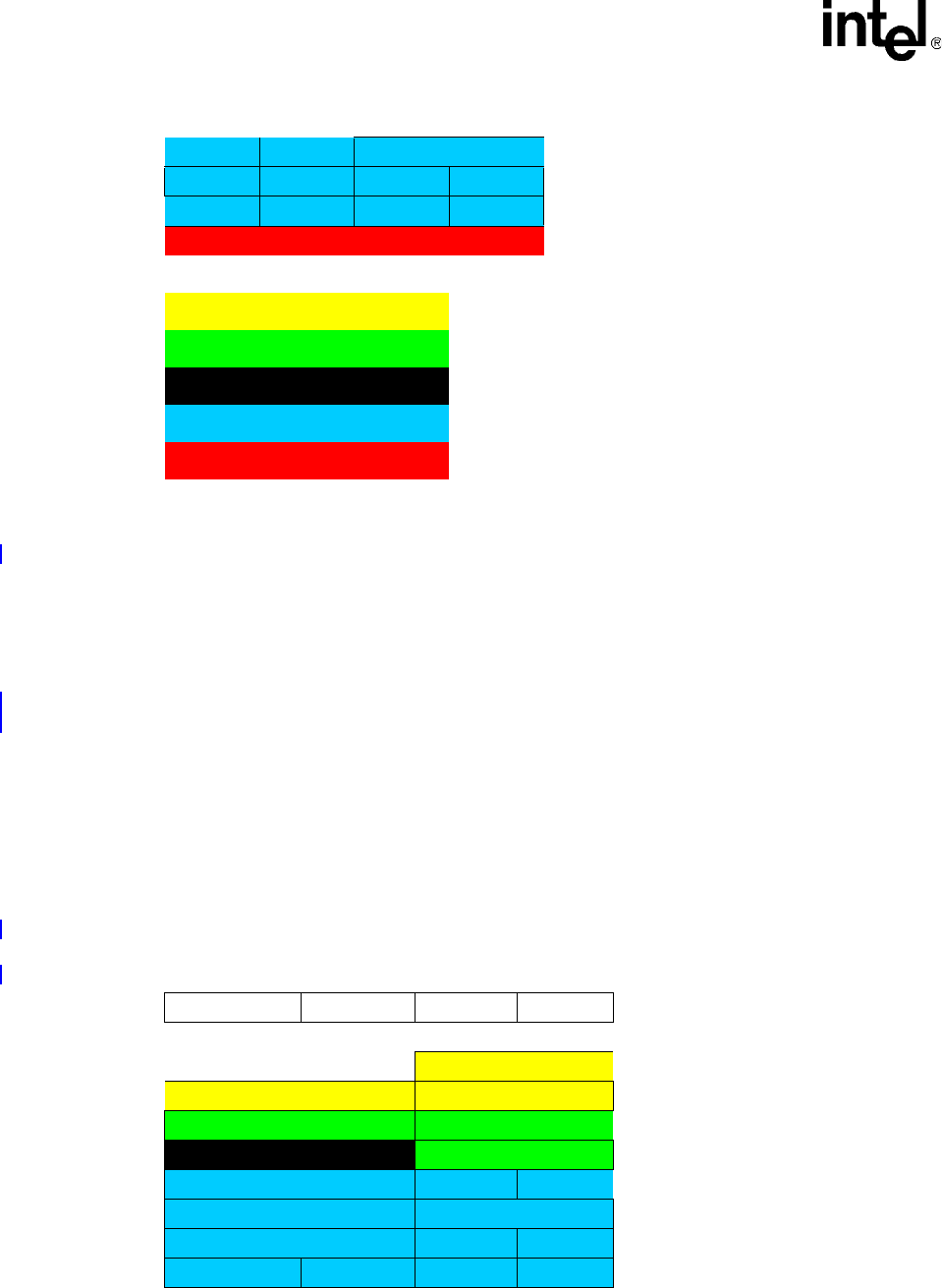

Detailed below is the typical receive case for 64-byte frame (60 + CRC).

Given an IX_OSAL_MBUF data pointer (ix_data) that is half-word-aligned, the NPE must transfer

the frame into main memory. The transactions the NPE AHB coprocessor generates depend on the

alignment and size of the transfer. For a 60-byte transfer, half-word-aligned, the NPE would

generate:

• One half-word transfer, half-word-aligned

• 14 word burst transfers, word-aligned

• One half-word transfer, half-word-aligned.

This will result in the following payload (see Figure 118) written to SDRAM from the Intel XScale

core (Address Coherent).

TTL Protocol Header Checksum

src-ip[0] src-ip[1] src-ip[2] src-ip[3]

dst-ip[0] dst-ip[1] dst-ip[2] dst-ip[3]

UDP/TCP Header

803.2 Destination MAC Address

802.3 Source MAC Address

802.3 Type

Internet Protocol

UDP/TCP Header

Figure 117. Ethernet Frame (Continued)(Big-Endian)

Figure 118. One Half-Word-Aligned Ethernet Frame (LE Address Coherent)

D0 D1 D2 D3

DA[1] DA[0]

DA[5] DA[4] DA[3] DA[2]

SA[3] SA[2] SA[1] SA[0]

Type/Len (swapped) SA[5] SA[4]

16-bit Total length (swapped) TOS ver/hlen

flag/Fragment offset (swap.) 16-bit Identif (swapped)

header checksum(swapped) Protocol TTL

src-ip[3] src-ip[2] src-ip[1] src-ip[0]