Intel

®

IXP400 Software

Access-Layer Components: Parity Error Notifier (IxParityENAcc) API

Programmer’s Guide IXP400 Software Version 2.0 April 2005

Document Number: 252539, Revision: 007 245

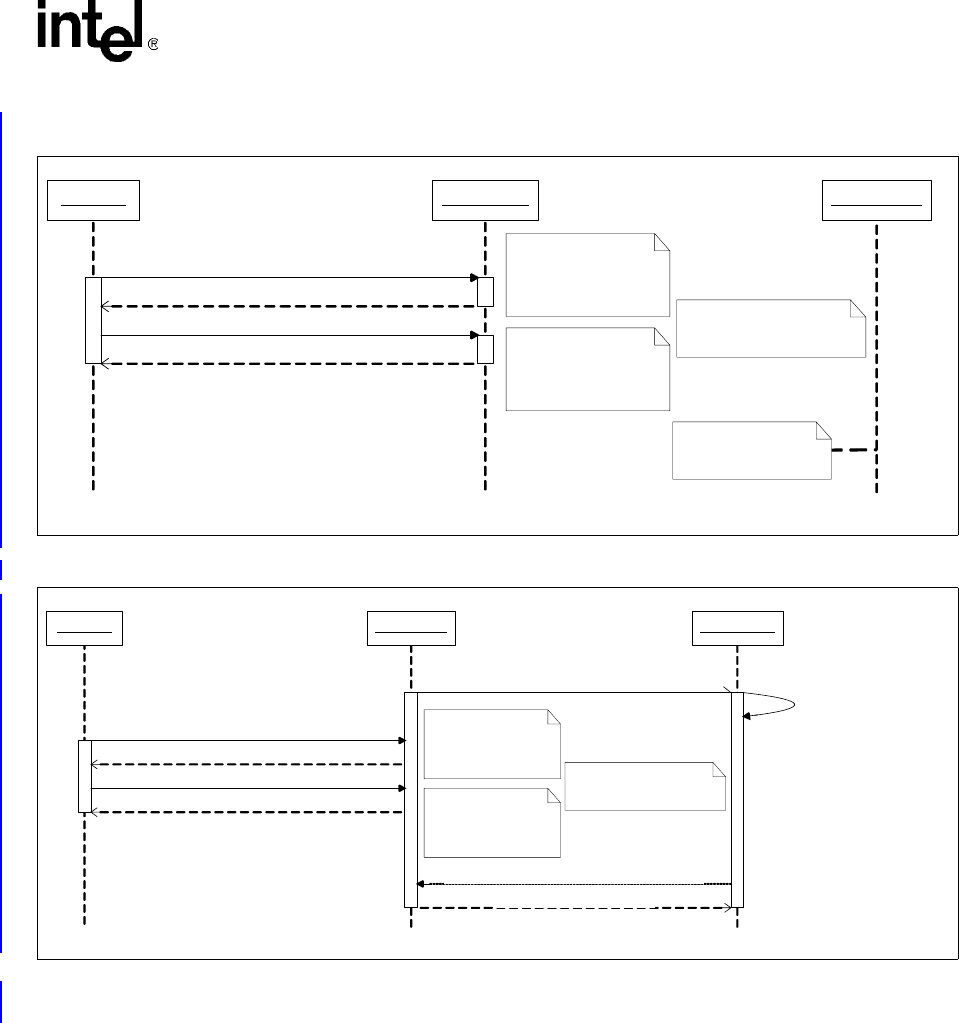

This scenario shown in Figure 83 can occur because the order in which the interrupts are triggered

for a parity error and a related data abort are not guaranteed.

Figure 81. Data Abort Caused by Parity Error

Figure 82. Parity Error Notification Followed by Related Data Abort

B4382-01

Data Abort IxParityENAcc Client Callback

IxParityENAccParityErrorContextGet(*pecMessage)

IxParityENAccParityErrorInterruptClear(*pecMessage)

IX_PARITYENACC_SUCCESS

IX_PARITYENACC_SUCCESS

Gets Parity

Interrupt Status:

Source = Multi-bit

Address = [Multi-bit]

Clear Parity

Interrupt:

Source = Multi-bit

Address = [Multi-bit]

{Multi-bit parity error

on MCU detected when

Data Abort occurred.}

Parity Interrupt will

not fire.

B4387-01

Data Abort IxParityENAcc Client Callback

IxParityENAccDAParityErrorContextGet(*pecMessage)

IxParityENAccDAParityErrorInterruptClear(*pecMessage)

(*IxParityENAccCallback)()

IxParityENAccParityErrorContextGet(*pecMessage)

DelayMaxDATriggerTime

IX_PARITYENACC_SUCCESS

IX_PARITYENACC_SUCCESS

IX_PARITYENACC_NOPARITY

Gets Parity

Interrupt Status:

Source = Multi-bit

Address = [Multi-bit]

Clear Parity

Interrupt:

Source = Multi-bit

Address = [Multi-bit]

{Multi-bit parity error

on MCU observed when

Data Abort occurred.}