Intel

®

IXP400 Software

Endianness in Intel

®

IXP400 Software

Programmer’s Guide IXP400 Software Version 2.0 April 2005

Document Number: 252539, Revision: 007 363

Control is transferred from the bootrom into VxWorks once it is downloaded via FTP. The MMU is

disabled during this transition and, as such, all SDRAM is in Address Coherent mode. The

SDRAM can only be converted to Data Coherent once the MMU is enabled. The MMU is enabled

in usrConfig code. The first opportunity to swap the SDRAM to Data Coherent is in hardware init

syshwInit0().

An example of how to place the SDRAM in Data Coherent mode while executing from this

SDRAM is the function named mmuARMXScalePBitSet() in sysLib.c.

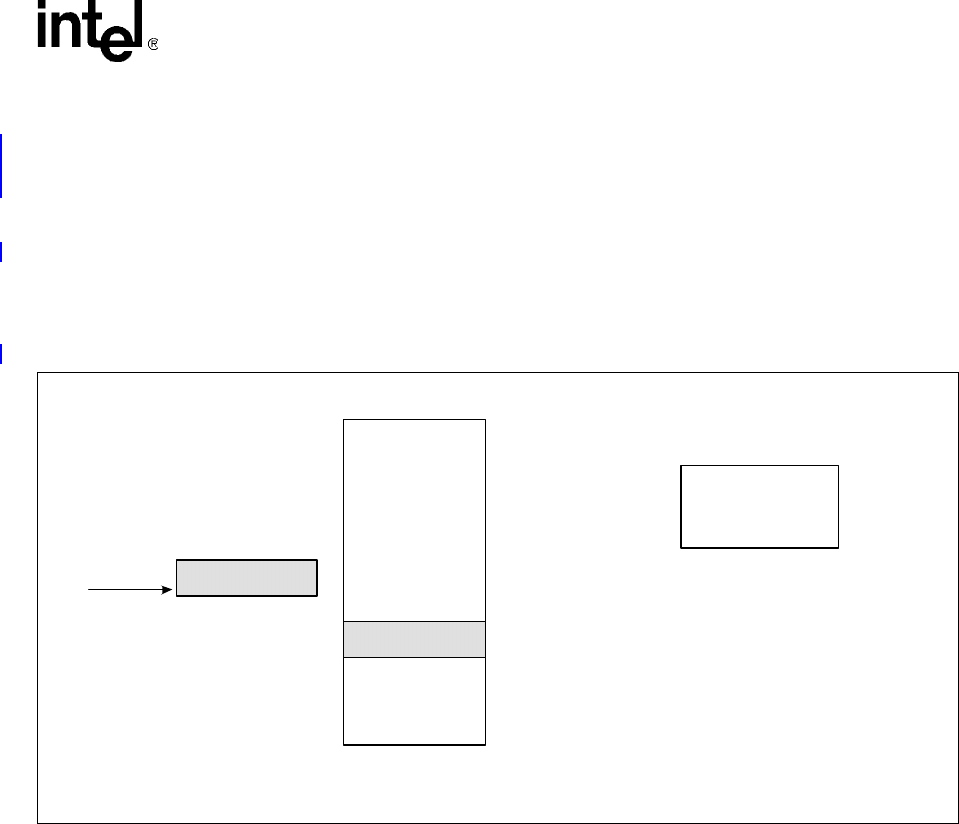

Figure 120 shows the related memory map.

The following is example pseudo code:

switchToDataCoherentSDRAM:

; Interrupts are disabled, in hwinit2().

Flush Cache (Instr & Data)

Drain Write buffers

Disable MMU

Invalidate Instr & Data cache

Invalidate TLB

Walk though all MMU SDRAM Large/Section entries , setting ‘P’ bit for all

entries.

Copy MMU enable code to Q-Manager scratch.

Perform LE endian swap on Region 1

Perform LE endian swap on Region 2

Set the P-Bit in MMU table walk

Enable Byte swap in expansion bus register

Jump to scratch memory location

Enable MMU

Wait for action to complete

Jump to switchToDataCoherentSDRAM – Label1

Label1:

Figure 120. VxWorks* Data Coherent Swap Code

B3789-001

Queue Manager Scratch

Execution Area

Region 2

Region 1

Top of SDRAM

sw itchToDataCoherentEnd

sw itchToDataCoherentSDRAM Label 1

sw itchToDataCoherentSDRAM() [start of function

Region 1, 2 will be

used in the pseudo

code below .

SDRAM Base

NOTE: Not to scale.