Intel

®

IXP400 Software

Access-Layer Components: HSS-Access (IxHssAcc) API

April 2005 IXP400 Software Version 2.0 Programmer’s Guide

214 Document Number: 252539, Revision: 007

13.7.2 Data Flow in Channelized Service

Data in the time slots configured as Voice64K/Voice56K types will be provided to the client via the

IxHssAcc channelized service. There are up to 32 such channels per HSS port. The channelized

service uses memory that is shared between the Intel XScale core and the NPEs. The client is

responsible for allocating the memory for IxHssAcc to transmit and receive data through the HSS

port.

For receive,

ixOsServCacheDmaAlloc() of the IxOSCacheMMU component can be used to create a

pointer to a pool of contiguous memory from the shared memory of the Intel XScale core and the

NPEs. The pointer to this Rx data pool needs to be a physical address because NPE will directly

write data into this memory area. The memory pool is divided into N circular buffers, one buffer

per channel. N is the total number of channels in service.

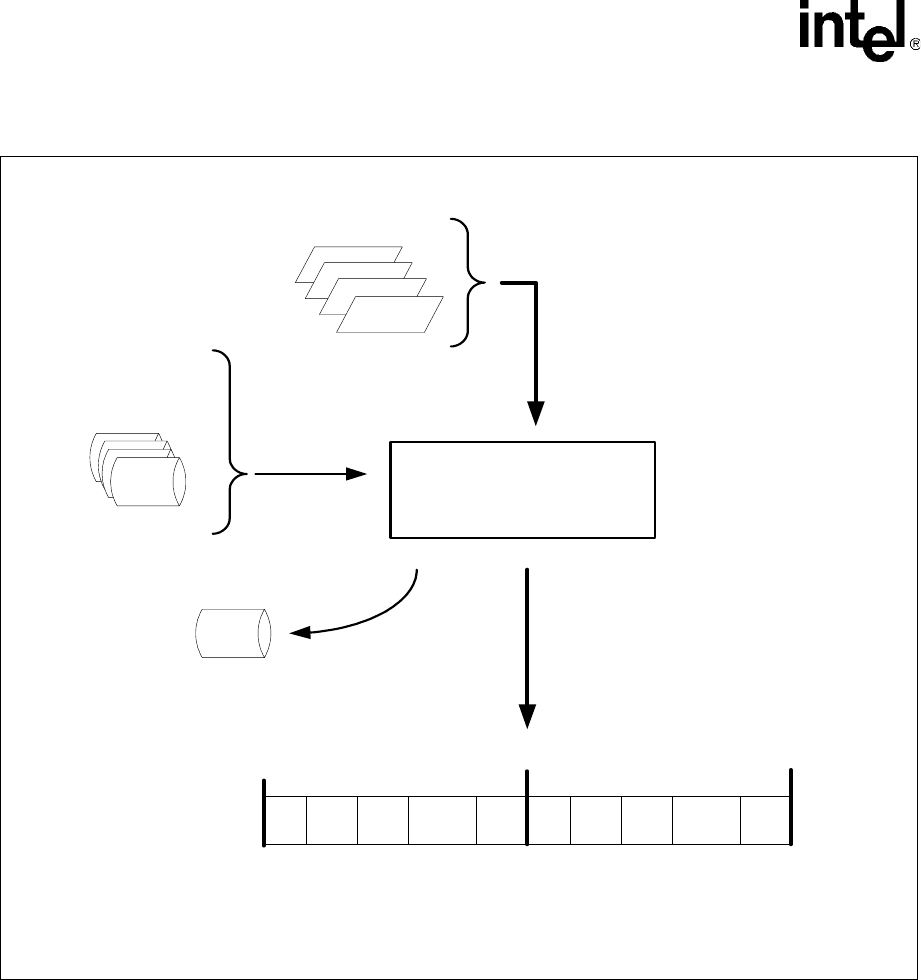

Figure 68. HSS Packetized Transmit Buffering

NPE-A

Hss Packetized Tx

Operation

2. Data (HDLC frame or RAW block)

for each packet-pipe read

from appropriate mbuf, specified

by descriptor

3. HDLC frame processing

performed on each

packet-pipe configured

for HDLC mode

HssPacketizedTx0 -

HssPacketizedTx3

queues

1. Descriptor read

from packet-

pipe-specific,

Tx queue

IXP_BUFs

4. Data transmitted

to HSS port

HssPacketizedTxDone

queue

5. Descriptor returned

when entire frame/

block sent.

F0-

TSa

F0-

TSb

F0-

TSc

...

F0-

TSz

Frame 0

F1-

TSa

F1-

TSb

F1-

TSc

...

F1-

TSz

Frame 1

...

HSS Port Serial Data Stream

(TSa, TSb, ... = timeslots configured as "HDLC")

B2383-03