Intel

®

IXP400 Software

Endianness in Intel

®

IXP400 Software

Programmer’s Guide IXP400 Software Version 2.0 April 2005

Document Number: 252539, Revision: 007 347

This chapter will provide an overview of the IXP4XX product line and IXC1100 control plane

processors capabilities related to endinness. For specific detail on the various capabilities and

hardware settings for the processors, refer to that processor’s specific DataSheet and Developer’s

Manual.

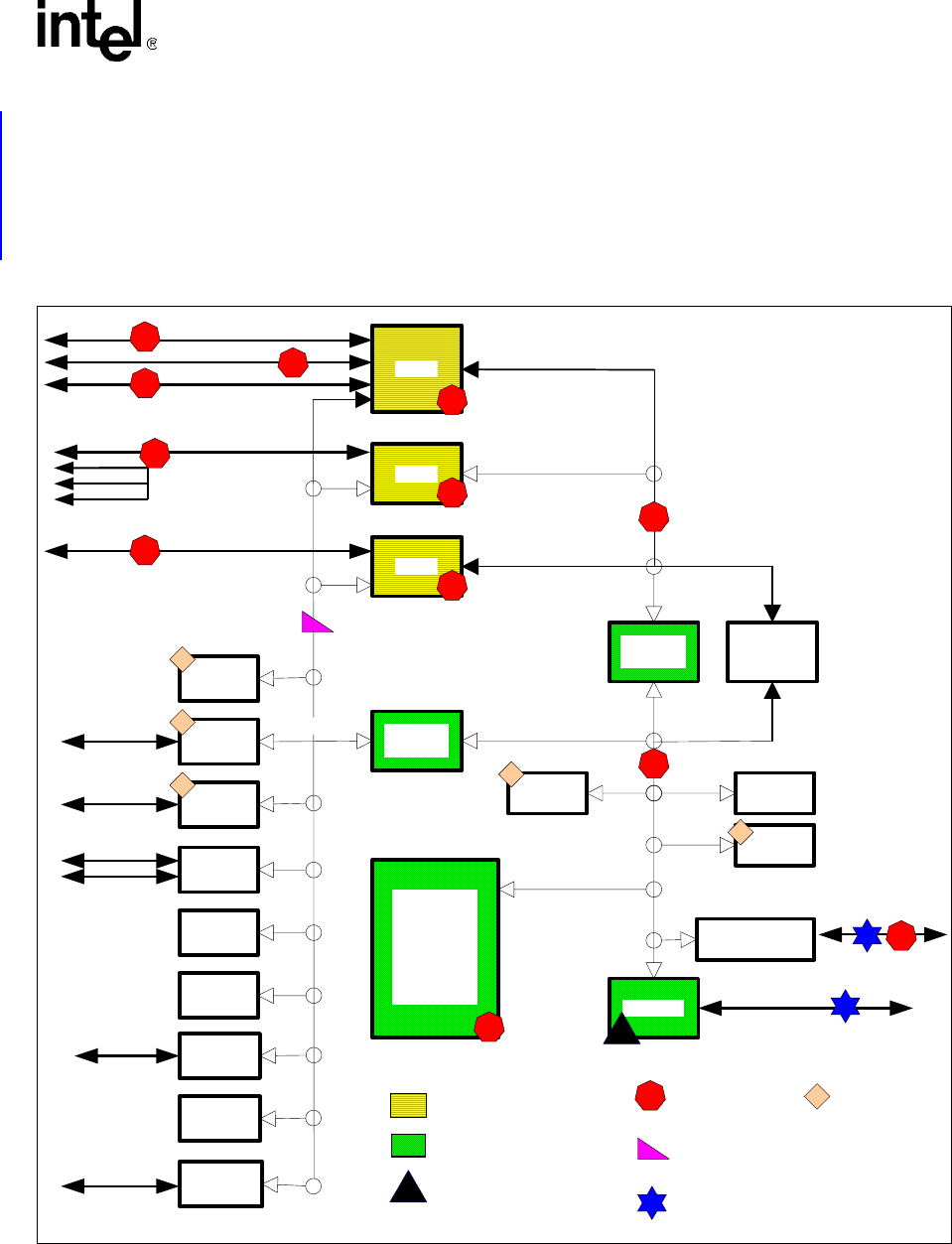

Figure 115 details the endianness of the different blocks of the IXP4XX processors when running a

Big-Endian software release.

Figure 115. Endianness in Big-Endian-Only Software Release

B3809-002

NPE A

NPE B

NPE C

USB v1.1

Device

AHB-APB

Bridge

AHB-AHB

Bridge

Memory

Controller

Queue

Manager

PCI 32/66

Intel XScale

®

Core

Data Cache

Instruction

Cache

South AHB

A

P

B

North AHB

Master on North AHB

Master on South AHB

MII/RMII 1

MII/RMII 1 (SMII 4)

HSS 1

HSS 0

UTOPIA 2

PCI

Big Endian

Endian Neutral

Little-Endian

Byte Swap On

Timers

GPIO

Interrupt

PMU

UARTs

IXP46X Only

SSP

I

2

C

IEEE

1588

PKE

Crypto

Expansion Bus

Controller

USB 2.0

Host