Intel

®

IXP400 Software

Endianness in Intel

®

IXP400 Software

Programmer’s Guide IXP400 Software Version 2.0 April 2005

Document Number: 252539, Revision: 007 359

The code below provides the read-out formation after the application of a conversion macro.

Effectively, the header comes in as Big-Endian and is then output as Little-Endian.

The following shows the IP header structure and outlines how the payload would be read from the

Intel XScale core in Little-Endian Data Coherent mode:

struct iphdr {

__u8version:4,hlen:4;/* Offset 0*/

__u8tos;/* Offset 1 byte*/

__u16tot_len;/* Offset 2 bytes*/

__u16id;/* Offset 4 bytes*/

__u16frag_off; /* Offset 6 bytes*/

__u8ttl;/* Offset 8 bytes*/

__u8protocol;/* Offset 9 bytes*/

__u16check;/* Offset 0xA bytes*/

__u32saddr;/* Offset 0xC bytes*/

__u32daddr;/* Offset 0xF bytes*/

/*The IP options start here. */

};

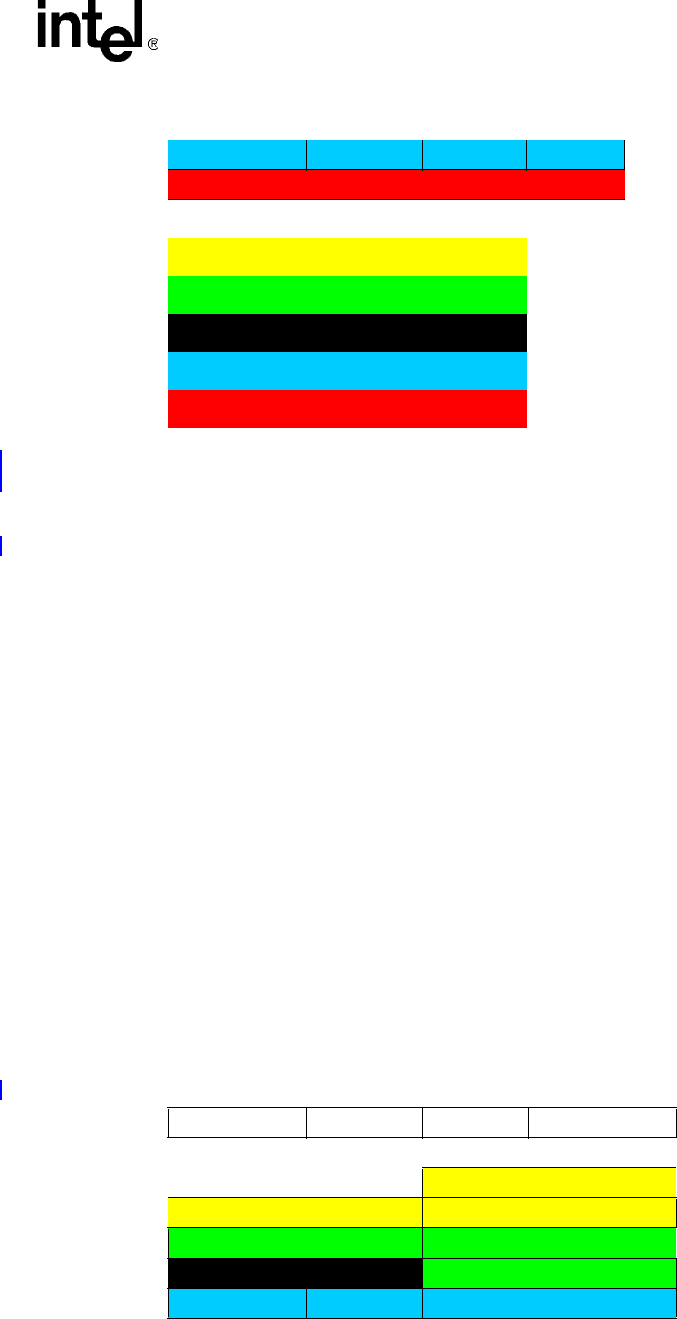

The Header contents assume the following reads: (See Figure 119)

• Half-word read at DA[1], half-word-aligned

• Word read at DA[2], word-aligned

• Word read at SA[3], word-aligned

• Half-word read type/len field, word-aligned

• Half-word read SA[5], half-word-aligned.

dst-ip[3] dst-ip[2] dst-ip[1] dst-ip[0]

UDP/TCP Header

803.2 Destination MAC Address

802.3 Source MAC Address

802.3 Type

Internet Protocol

UDP/TCP Header

Figure 118. One Half-Word-Aligned Ethernet Frame (Continued)(LE Address Coherent)

Figure 119. Intel XScale

®

Core Read of IP Header (LE Data Coherent)

D0 D1 D2 D3

DA[1] DA[0]

DA[5] DA[4] DA[3] DA[2]

SA[3] SA[2] SA[1] SA[0]

Type/Len (swapped) SA[5] SA[4]

ver/hlen TOS 16-bit Total length (swapped)