Intel

®

IXP400 Software

Access-Layer Components: Queue Manager (IxQMgr) API

April 2005 IXP400 Software Version 2.0 Programmer’s Guide

266 Document Number: 252539, Revision: 007

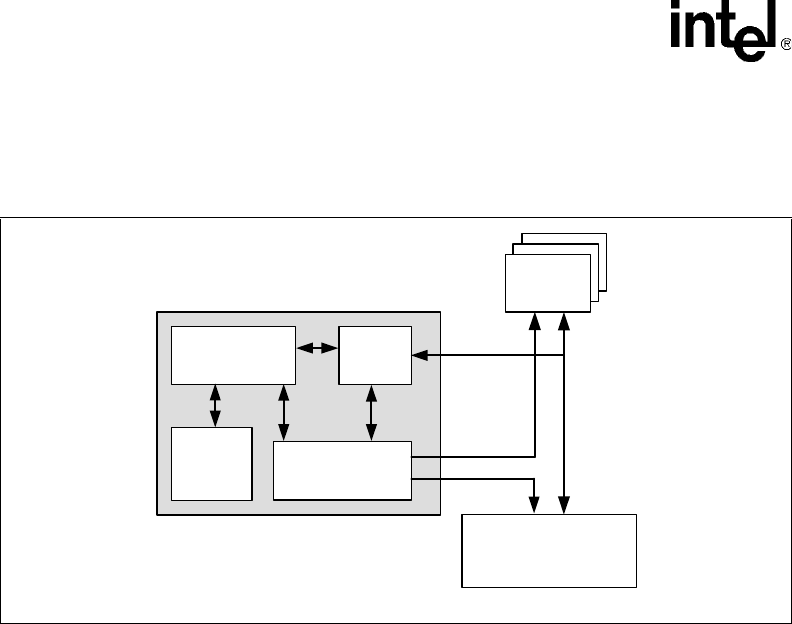

18.3 Features and Hardware Interface

The IxQMgr provides a low-level interface for configuring the AQM, which contains the physical

block of static RAM where all the data structures (queues) for the IxQMgr reside. The AQM

provides 64 independent queues in which messages, pointers, and data are contained. Each queue is

configurable for buffer and entry size and is allocated a status register for indicating relative

fullness.

The AQM maintains these queues as circular buffers in an internal, 8-Kbyte SRAM. Status flags

are implemented for each queue. The status flags for the lower 32 queues are transmitted to the

NPEs via the flag data bus. Two interrupts — (QM1) one for the lower 32 queues and (QM2) one

for the upper 32 queues — are used as queue status interrupts.

The AHB interface provides for complete queue configuration, queue access, queue status access,

interrupt configuration, and SRAM access.

IxQMgr provides the following services:

• Configures AQM hardware queues.

Configuration of a queue includes queue size, entry size, watermark levels, and interrupt-

source-select flag. IxQMgr checks the validity of the configuration parameters and rejects any

configuration request that presents invalid parameters.

• Allows callbacks to be registered for each queue. This is also referred as notification callback.

• Enables and disables notifications for each queue.

• Sets the priority of a callback.

• Provides queue-notification source-flag select.

— For queues 0-31, the notification source is programmable as the assertion or de-assertion

of one of four status flags: Empty, Nearly Empty, Nearly Full, and Full.

Figure 89. AQM Hardware Block

NPE

AHB

Flag Bus

AHB Queue Manager

Queue

Buffer

SRAM

Queue

Control

AHB

Slave

Config/Status

Registers

Int

Intel XScale® Core

B2415-02