Intel

®

IXP400 Software

Operating System Abstraction Layer (OSAL)

Programmer’s Guide IXP400 Software Version 2.0 April 2005

Document Number: 252539, Revision: 007 323

The OSAL layer also provides APIs for dealing with the following situations:

• Transparently accessing I/O-memory-mapped hardware in different endian modes

• Transparently accessing SDRAM memory between any endian type and big endian, for the

purpose of sharing data with big-endian auxiliary processing engines

The OSAL layer supports the following endianness modes:

• Big endian

• Little endian

• Little endian address coherent where

— Core is operating in little endian mode but the bus addresses are swapped

— 32-bit word accesses are made automatically in big endian mode

— Byte and 16-bit half-word addresses are swapped (address XOR 3)

• Little endian, data coherent where,

— Core is operating in little endian mode but the bus data is swapped

— Byte accesses are made automatically in big endian mode

— 32-bit word and 16-bit half-word values are swapped

In little endian mode, users must specify coherency modes before using the IO/Memory access

macros (for example, IX_OSAL_READ_LONG, IX_OSAL_WRITE_LONG). This can be

performed by declaring Little Endian Coherency mode in the customized mapping declarations

under os/vxworks/include/platforms/ixp400/.

Table 64 provides an overview of the I/O memory and endianness support module.

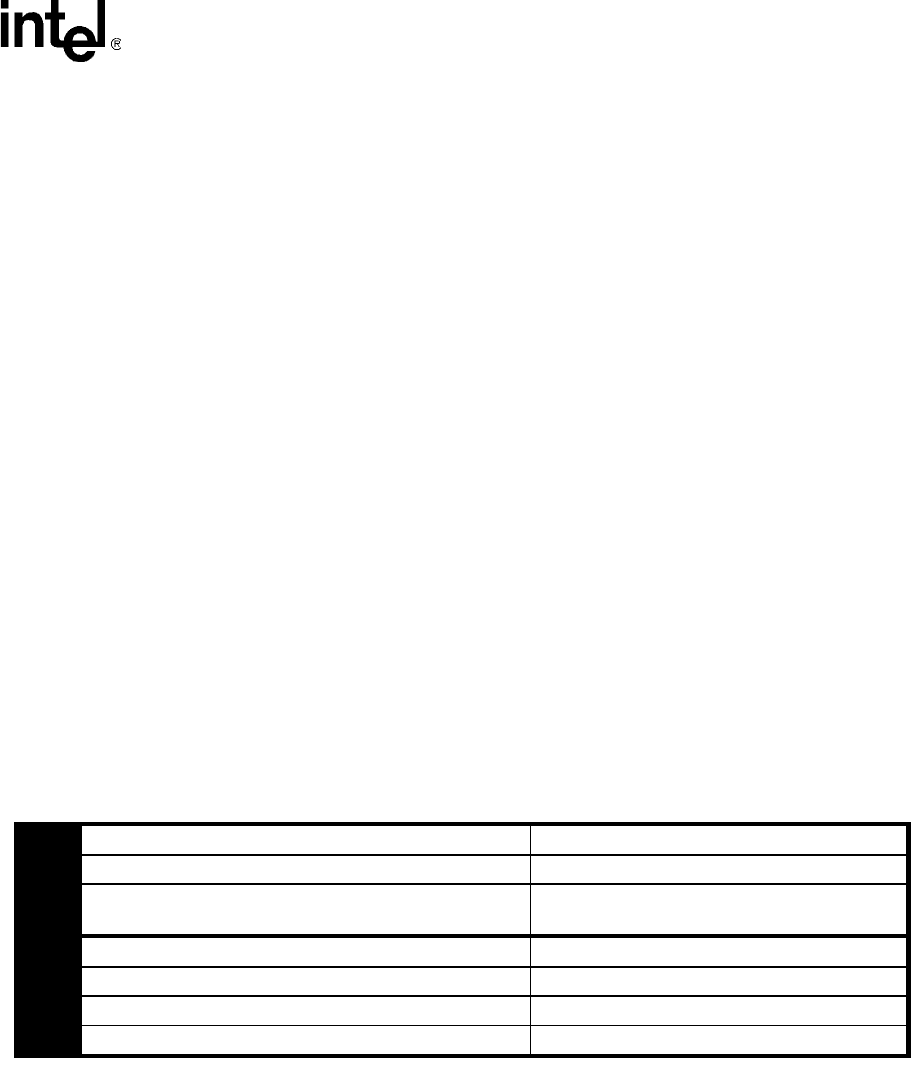

Table 64. OSAL I/O Memory and Endianness Interface (Sheet 1 of 2)

IX_OSAL_COMPONENT_MAPPING select endianness mapping type

IX_OSAL_MEM_MAP_TYPE select static/dynamic I/O mapping

Defines

required

IX_OSAL_SDRAM_ENDIANNESS select SDRAM endianness

IX_OSAL_MEM_MAP map I/O memory

IX_OSAL_MEM_UNMAP unmap I/O memory

IX_OSAL_MMAP_PHYS_TO_VIRT physical to virtual translation

I/O

Mapping

IX_OSAL_MMAP_VIRT_TO_PHYS virtual to physical translation