Intel

®

IXP400 Software

Access-Layer Components: Time Sync (IxTimeSyncAcc) API

Programmer’s Guide IXP400 Software Version 2.0 April 2005

Document Number: 252539, Revision: 007 287

The IEEE 1588 Hardware Assist block can also be set explicitly to handle timestamping for all

messages detected on a channel, as determined by the detection of an Ethernet Start of Frame

Delimiter (SFD). In this scenario, the snapshot registers containing the timestamps will not be

locked. This usage model is useful for network traffic analysis applications.

Besides the timestamps, the hardware will also capture the UUID and Sequence ID for the

Delay_Req and Sync messages received in Master and Slaves modes, respectively.

An auxiliary timestamp feature is also provided in the IEEE 1588 Hardware Assist block, allowing

for the capture of system time to be trigger via the GPIO pins. The slave or master timestamp will

be captured when the appropriate GPIO pins (8 and 7, respectively) are triggered by the Intel

XScale core or an external device. When these timestamps are captured, the Intel XScale core will

be notified through interrupts or sets event flags, depending on whether the interrupts are masked

off or not.

Note: On the IXDP465 platform, the Auxiliary Timestamp signal for slave mode is tied to GPIO pin 8.

This signal is software routed by default to PCI for backwards compatibility with the IXDP425 /

IXCDP1100 platform. This routing must be disabled for the auxiliary slave time stamp register to

work properly. Refer to the Intel

®

IXDP465 Development Platform User’s Guide or the BSP/LSP

documentation for more specific information.

The hardware assist can be reset by software and will reflect the same state as can be observed on

power-on reset. Table 49 summarizes the default behavior of certain hardware features upon

power-on reset or software-initiated reset.

Upon reset, the system time, frequency scaling value and target time are all set to zero. Thus, at the

time of power-on reset and software-initiated reset, the frequency scaling value will not increment.

This value needs to be set to a non-zero value to allow the system time to increment. The UUID

and Sequence ID are also cleared to zeros. A UUID with value zero is treated as invalid.

IPv6 and VLAN-Tagged Ethernet Frames

The IEEE 1588 Hardware Assist block does not support the IPv6 protocol. It verifies that the

Ethernet frame contains an IPv4 packet by checking for a value of 0x45 in the first byte of the IP

datagram header. 0x45 represents a value of 4 in the

Version field and a 20-byte IP header length.

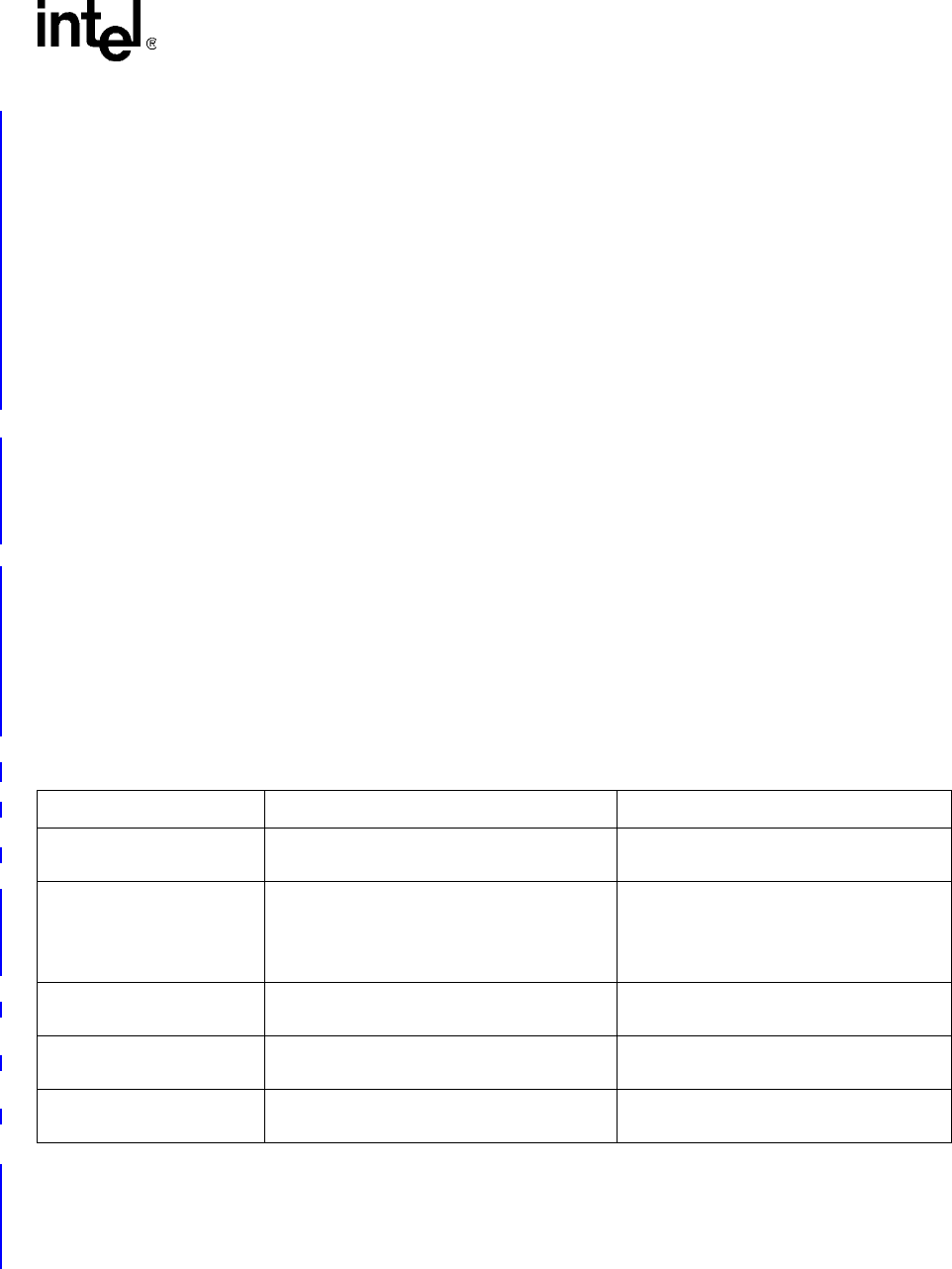

Table 49. Default IEEE 1588 Hardware Assist Block States upon Hardware/Software Reset

Hardware Feature Options Default State

Channel Mode

- Master

- Slave

Each channel operates in slave mode.

TimeStamp

- Sync and Delay_Req messages only

- All IPv4 packets

Timestamp is taken for valid

Sync and

Delay_Req messages and locked in the

receive and transmit snapshot registers,

respectively, since the default channel mode

of operation is slave.

Auxiliary Master Mode

Snapshot Interrupt Mask

- Enabled

- Disabled

Disabled

Auxiliary Slave Mode

Snapshot Interrupt Mask

- Enabled

- Disabled

Disabled

Target Time Interrupt Mask

- Enabled

- Disabled

Disabled