Intel

®

IXP400 Software

Access-Layer Components: Parity Error Notifier (IxParityENAcc) API

Programmer’s Guide IXP400 Software Version 2.0 April 2005

Document Number: 252539, Revision: 007 239

• Parity Error Recovery

• Parity Error Prevention

This section summarizes the high-level activities involved with these high-level tasks, and then

presents specific usage scenarios.

16.4.1 Summary Parity Error Notification Scenario

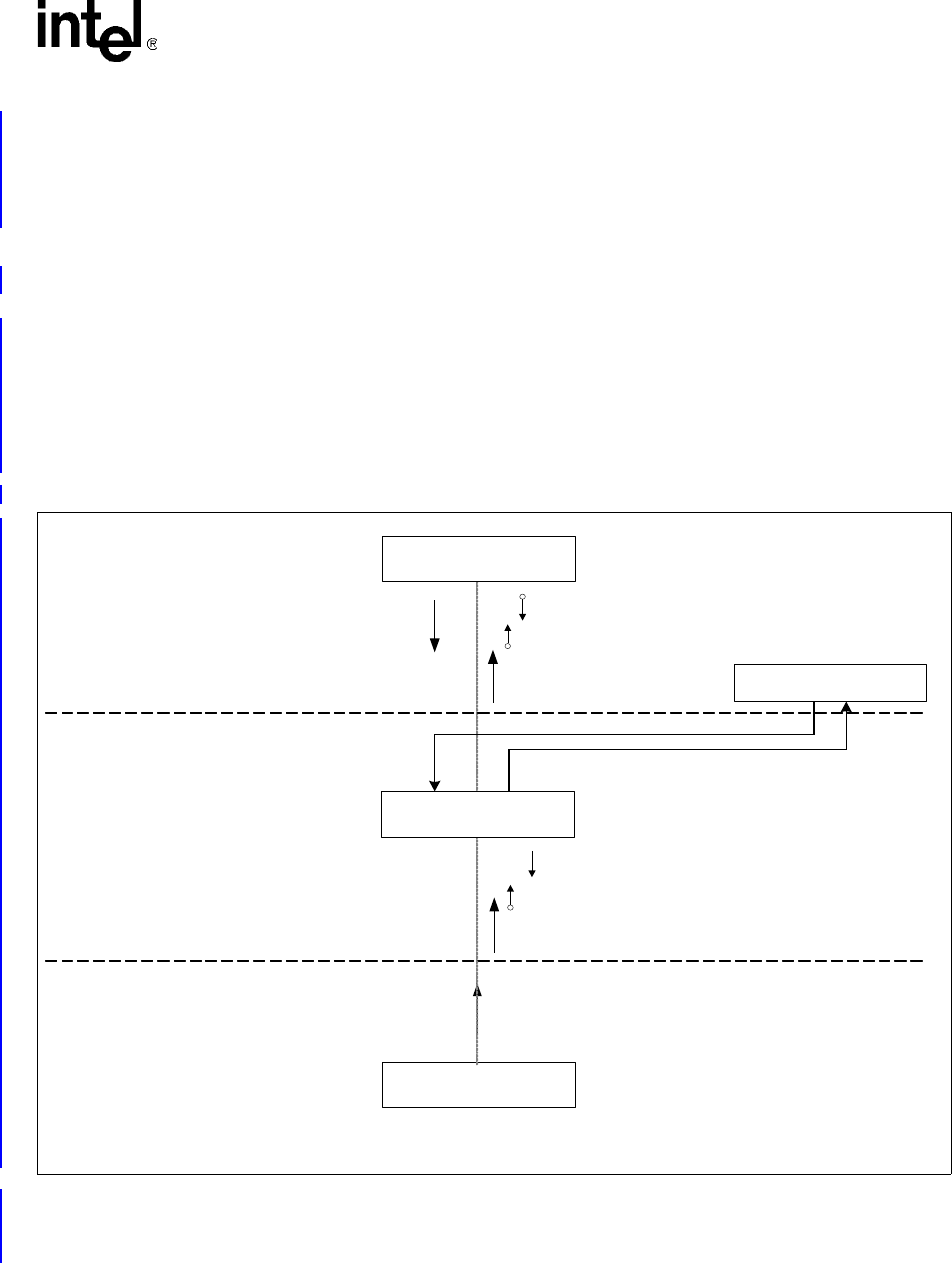

The interface between the client application and IxParityENAcc is explained in detail in the API

source-code documentation. However, the following important scenario (shown in Figure 76)

captures the usage of interface(s) by the client application.

The parity error context is represented with the data flow direction arrow with an open bubble at

the end. The numbers at the beginning of each of the APIs and internal steps define their execution

sequence in that order.

1. The client application will initialize the component.

2. After initialization the client application will register callback and configure the parity error

detection for the specified hardware blocks.

Figure 76. Parity Error Notification Sequence

B4384-01

Client Application

Access-Layer

4: (*ixParityENAccCallback) (void)

3: Parity Error Interrupt

Client

Interrupt Controller/

Hardware Block

Client Callback Routine

(Parity Error Recovery)

Hardware

3a: Invoke Parity Error Interrupt Handler

5b : Fetch the parity error context

1: ixParityENAccInit (void)

2. ixParityENAccCallbackRegister(parityErrNfyCallBack)

ixParityENAccParityDetectionConfigure(*hwParityConfig)

5. ixParityENAccParityErrorContextGet(*pecMessage)

6. ixParityENAccParityErrorInterruptClear(*pecMessage)

2b: Save Callback

3b: Get Callback

6b : interrupt clear or mask off

IxParityENAcc