Intel

®

IXP400 Software

Endianness in Intel

®

IXP400 Software

April 2005 IXP400 Software Version 2.0 Programmer’s Guide

352 Document Number: 252539, Revision: 007

27.4.3.5 PCI Bus Swap

The PCI controller has a byte lane swapping feature. The “swap” is controlled via the PCI_CSR

register’s PDS and ADS bits within the PCI controller. The swap feature needs to be enabled if the

Intel XScale core is in Big-Endian mode or Data Coherent Little-Endian mode. For further details,

refer to the processor’s specific DataSheet and Developer’s Manual.

Note: The PCI_CSR bits on the IXP46X product line are refered to as PBS and ABS. However, they are

in the same location as previous IXP4XX product line and IXC1100 control plane processors.

27.4.3.6 Summary of Silicon Controls

Table 65 summarizes the device selections and their behavior.

27.4.4 Silicon Versions

Available hardware endianess controls vary by the stepping or product family of the processor.

Identification of silicon version is indicated by markings on the devices themselves, or by

accessing a register on the chip. Further details regarding this are available in the Intel

®

IXP400

Software Programmer’s Guide and the processor’s specific DataSheet .

IXP425 network processor A-0 Stepping and IXC1100 control plane processor A-0

Stepping

This processor version supports:

• Big-Endian

• Little-Endian Address Coherency

The A-0 stepping part numbers are shown in Table 66:

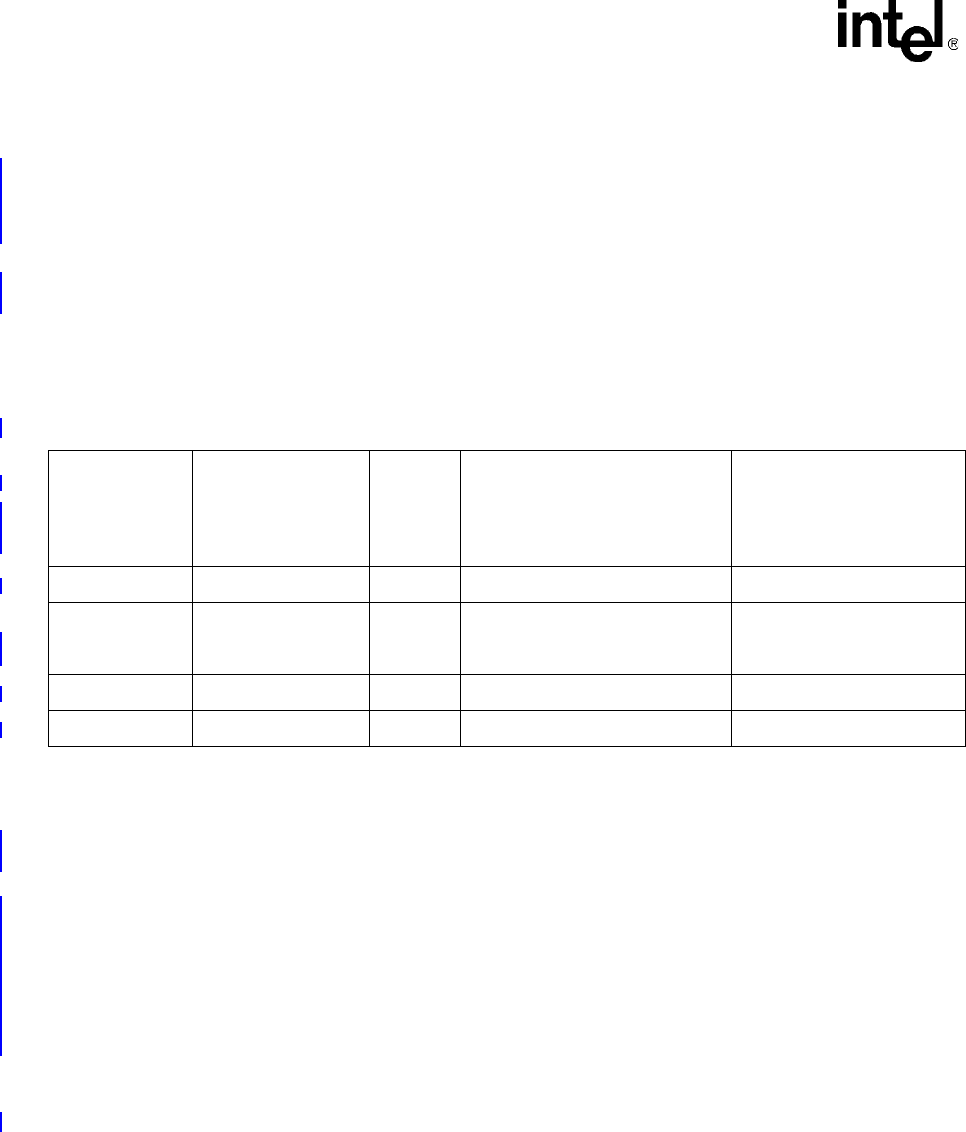

Table 65. Endian Hardware Summary

Intel XScale

®

Core

Endianness

[1 = Big-

Endian]

Expansion Bus

Config Register

[BYTE_SWAP_EN]

MMU ‘P’

Bit

Intel XScale

®

Core endianness

and it’s interaction with the AHB

bus

PCI Bus Swap

Enabled =

PCI_CSR_PDS=1,

PCI_CSR_ADS =1

1 X X Big-Endian Enabled

0 1 1 Little-Endian – Data Coherent

Enabled, and PCI Bus space

must be Data Coherent

(0x48xx,xxxx)

0 1 0 Little-Endian – Address Coherent Disabled

0 0 X Little-Endian – Address Coherent Disabled