Intel

®

IXP400 Software

Access-Layer Components: Synchronous Serial Port (IxSspAcc) API

April 2005 IXP400 Software Version 2.0 Programmer’s Guide

276 Document Number: 252539, Revision: 007

• select SPI SCLK phase – phase of SCLK starts with one inactive cycle and ends with ½

inactive cycle or SCLK starts with ½ inactive cycle and ends with one inactive cycle (only

used in SPI format)

• select Microwire control word format – 8 or 16 bits

• enable/disable the SSP serial port hardware

This component also provides status and statistics for:

• SSP state – busy or idle

• Transmit FIFO level – 0 to 16 frames

• Receive FIFO level – 0 to 16 frames

• Transmit FIFO hit or below its threshold

• Receive FIFO hit or exceeded its threshold

• Receive FIFO overrun.

• Statistics for frames received, frames transmitted, and number of overrun occurrences.

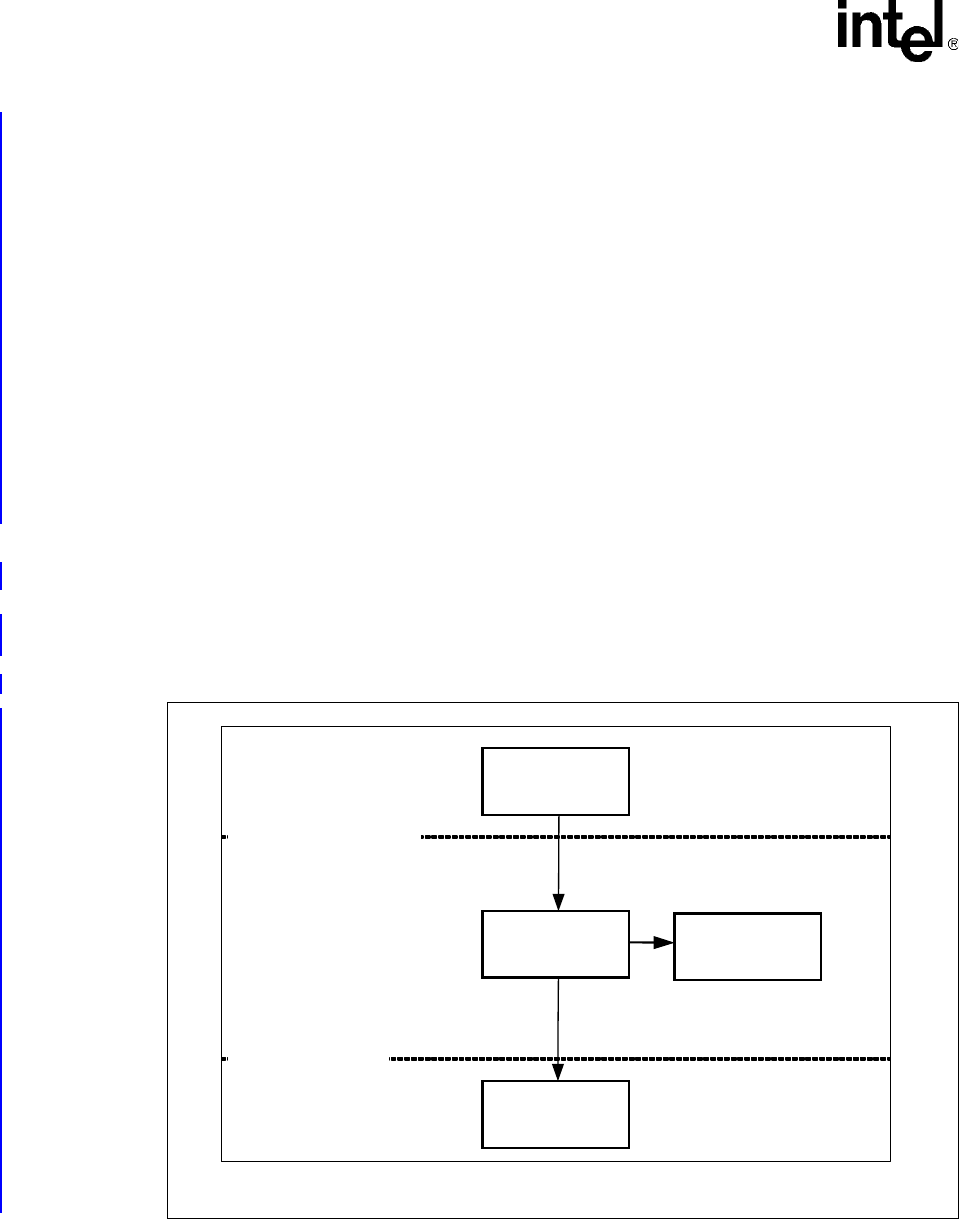

19.3.2 Dependencies

IxSspAcc is dependent on the capability provided by the SSP serial port hardware. IxOSAL

provides OS independency.

Figure 92. IxSspAcc Dependencies

B4388-01

Access-Layer Interface

Hardware Interface

Client Application

IxOSAL

IxSspAcc

SSP Port