8 - 34 8 - 34

MELSOFT

8 ACCESSIBLE DEVICES AND RANGES

8.9 For CPU Board Communication

This section provides the accessible devices and accessible ranges for CPU board

communication.

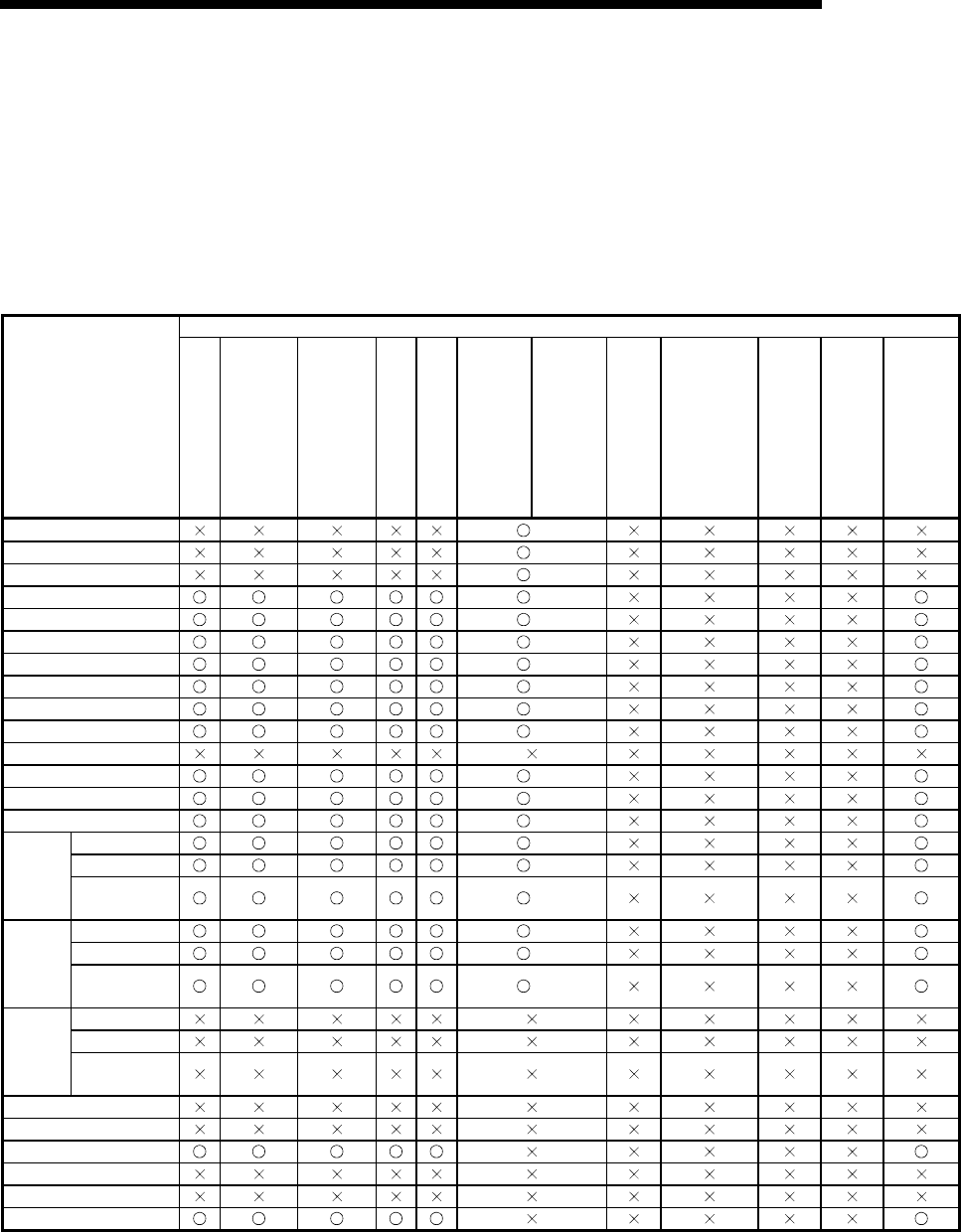

8.9.1 Accessible devices

The following table indicates the accessible devices for CPU board communication.

Access Target

Device

(Device Name)

A1N

A0J2H

A1S(-S1)

A1SH

A1SJ(H)

A2C(J)

A2N(-S1)

A2S(-S1)

A2SH(-S1)

A1FX

A2A(-S1)

A2U(-S1)

A2US(-S1)

A2AS

(-S1/-S30)

A2USH-S1

Q02(H)-A

Q06H-A

A3N

A3A

A3U

A4U QnACPU

QCPU

(Q mode)

LCPU Q12DCCPU-V QSCPU FXCPU

Motion

controller

CPU

Function input (FX) *1

Function output (FY) *1

Function register (FD) *1

Special relay (SM) *1

Special register (SD) *1

Input relay (X) *1

Output relay (Y) *1

Internal relay (M) *1

Latch relay (L) *1

Annunciator (F) *1

Edge relay (V)

Link relay (B) *1

Data register (D) *1

Link register (W) *1

Contact (TS) *1

Coil (TC) *1

Timer

(T)

Present value

(TN)

*1

Contact (CS) *1

Coil (CC) *1

Counter

(C)

Present value

(CN)

*1

Contact (SS)

Coil (SC)

Retentive

timer

(ST)

Present value

(SN)

Link special relay (SB)

Link special register (SW)

Step relay (S)

Direct input (DX)

Direct output (DY)

Accumulator (A)

*1: Access to QCPU (Q mode) cannot be made.

When making access to QnACPU, the range is equivalent to that of AnACPU.

(To the next page)