Theory of Operation

3-48

2715 Spectrum Analyzer Service Manual

MKR2_LT. This signal becomes active (high) at any access to the Marker 2 port

addresses (I/O port addresses 0xFE00 through 0xFFFF). This signal also causes

the UPREQ signal to become active.

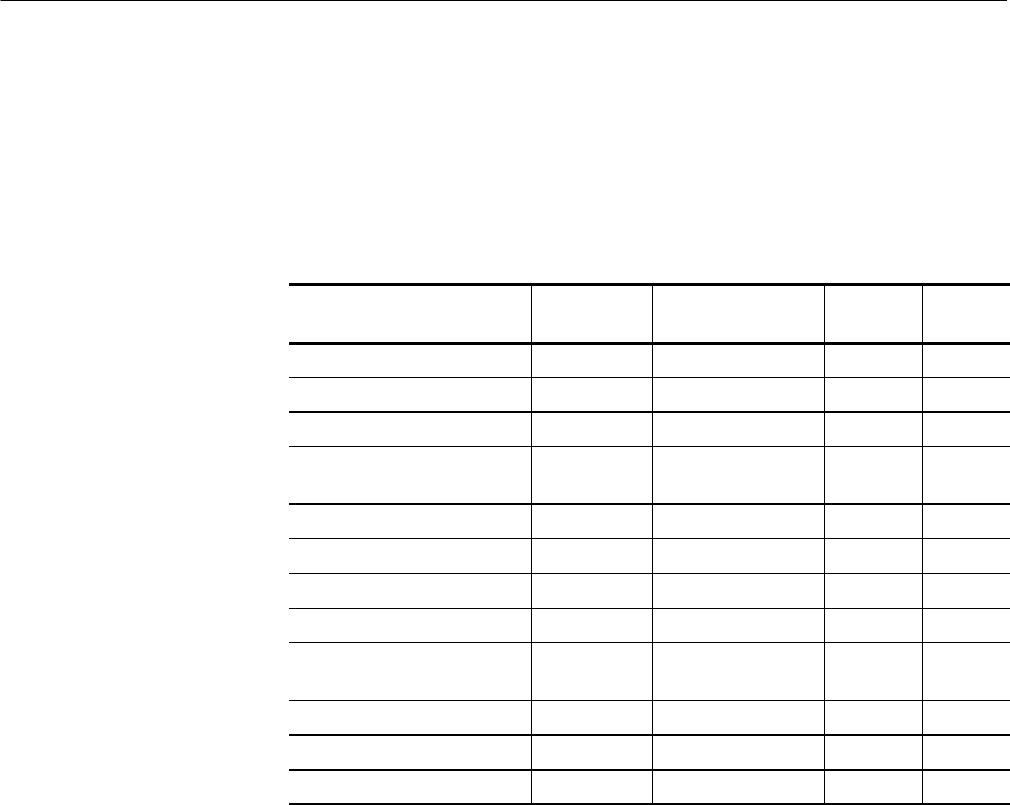

Table 3 --11 is the memory map for the Display Storage board.

Table 3- 11: Memory Map for the Display Storage Board

Name

Total Num-

ber of Bytes

Address

Range Decoded

Signal

Name

Memory

Type

Control Registers (512 bytes) 0x0FA000x0FBFF PORTVEC I/O Port

Marker 1 Position (512 bytes) 0x0FC000x0FDFF MKR1_LT I/O Port

Marker 2 Position (512 bytes) 0x0FE000x0FFFF MKR2_LT I/O Port

Nonvolatile

Waveform Storage

(28,672 bytes) 0x380000x3EFFF UPREQ Memory

Storage - Waveform A (512 bytes) 0x3F0000x31FFF UPREQ Memory

Storage - Waveform B (512 bytes) 0x3F2000x3F3FF UPREQ Memory

Storage - Waveform C (512 bytes) 0x3F4000x3F5FF UPREQ Memory

Storage - Waveform D (512 bytes) 0x3F6000x3F7FF UPREQ Memory

Storage - Text Page 1

(Readouts)

(512 bytes) 0x3F8000x3F9FF UPREQ Memory

Storage - Text Page 2 (512 bytes) 0x3FA000x3FBFF UPREQ Memory

Storage - Text Page 3 (512 bytes) 0x3FC000x3FDFF UPREQ Memory

Storage - Text Page 4 (512 bytes) 0x3FE000x3FFFF UPREQ Memory

The following paragraph describes a typical CPU read or write of the Display

Storage board.

The CPU begins by presenting the read or write address to the Display Storage

board on the BA<19..0> lines. The upper eleven address lines (BA<19..9>) are

fed into the address decoder PAL, U29. If the address is inside the range for the

Display Storage board the UPREQ signal becomes high, and the appropriate

enable signal becomes active (PORTVEC, MKR1_LT, or MKR2_LT). The

UPREQ signal is a request for access to the Display Storage board, and it feeds

the RAM arbitrator. As soon as the UPREQ signal becomes active, the CPU

BWAIT_L signal is pulled low, forcing the CPU into a wait state. The CPU will

remain in this wait state until the RAM arbitrator allows the CPU to access the

board. The RAM arbitrator will bring the UPGRNT_L signal low, when it is

ready to allow the CPU to access the Display Storage board. When UPGRNT_L

goes low, the data bus transceiver, U22, is enabled as well as the RDEN and

WREN signals to the rest of the Display Storage board.