SA-1110 Developer’s Manual 111

System Control Module

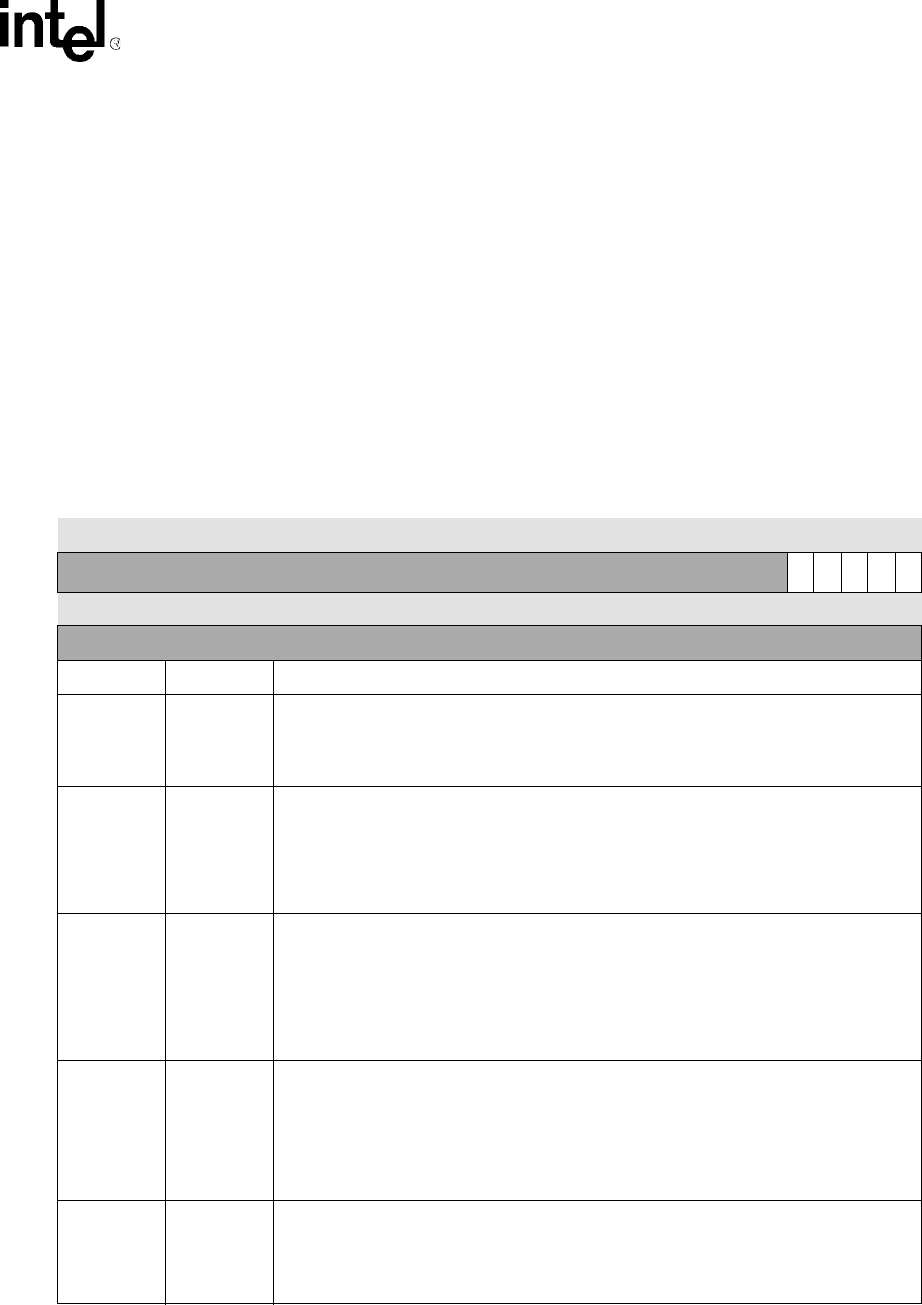

9.5.7.5 Power Manager Sleep Status Register (PSSR)

PSSR contains five status flags. The software sleep status flag is set when sleep mode is entered as

a result of the sleep force (SF) control bit being set by the CPU. The battery fault status bit is set

any time the BATT_FAULT pin is asserted (even when the SA-1110 is already in sleep mode). The

VDD fault status bit is set only when the assertion of the VDD_FAULT pin causes sleep mode

invocation ( that is, if the force sleep bit is asserted and sleep mode is entered followed by the

assertion of the VDD_FAULT pin, the VDD fault status bit is not set). Hardware (power-on) reset

clears PSSR, but the sleep mode reset, software reset, and watchdog reset do not affect this register.

The peripheral hold and DRAM hold bits indicate that those two interfaces retain the same value as

during sleep until these bits are cleared.

The five status flags are cleared when a one is written to them. Writing zero to any status bit has no

effect. Reserved bits read as zeros and are unaffected by writes. The following table shows the

PSSR.

0h 9002 0004 PSSR Read/Write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

PH

DH

VFS

BFS

SSS

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

0SSS

Software sleep status.

0 – Chip has not been placed in sleep mode by setting the sleep force (SF) control bit since

it was last cleared by reset or by the CPU.

1– Chip was placed in sleep mode by setting the sleep force (SF) control bit.

1BFS

Battery fault status.

0 – BATT_FAULT pin has not been asserted since it was last cleared by a hardware reset

or by the CPU.

1 – BATT_FAULT pin has been asserted.

NOTE: This bit will be set by the assertion of BATT_FAULT while the SA-1110 is in sleep

mode."

2VFS

VDD fault status.

0 – VDD_FAULT pin has not been asserted since it was last cleared by a hardware reset or

by the CPU.

1 – VDD_FAULT pin was asserted in run or idle mode and caused the chip to enter sleep

mode.

NOTE: This bit will not be set by the assertion of VDD_FAULT while the SA-1110 is in

sleep mode.

3DH

DRAM control hold.

This bit is set upon exit from sleep mode and indicates that the nRAS/nSDCS[3:0] and

nCAS/DQM[3:0] continue to be held low and that the DRAMs are still in self-refresh mode.

This bit should be cleared by the processor (by writing a one to it) before the DRAM

interface has been configured and any DRAM access is attempted. The nRAS/nSDCS and

nCAS/DQM lines are released when this bit is cleared. This bit is cleared on hardware

reset.

4PH

Peripheral control hold.

This bit is set upon exit from sleep mode and indicates that the peripheral pins are being held

in their sleep state. This bit should be cleared by the processor (by writing a one to it) after the

peripheral interfaces have been configured but before they are actually used by the

processor.