184 SA-1110 Developer’s Manual

Memory and PC-Card Control Module

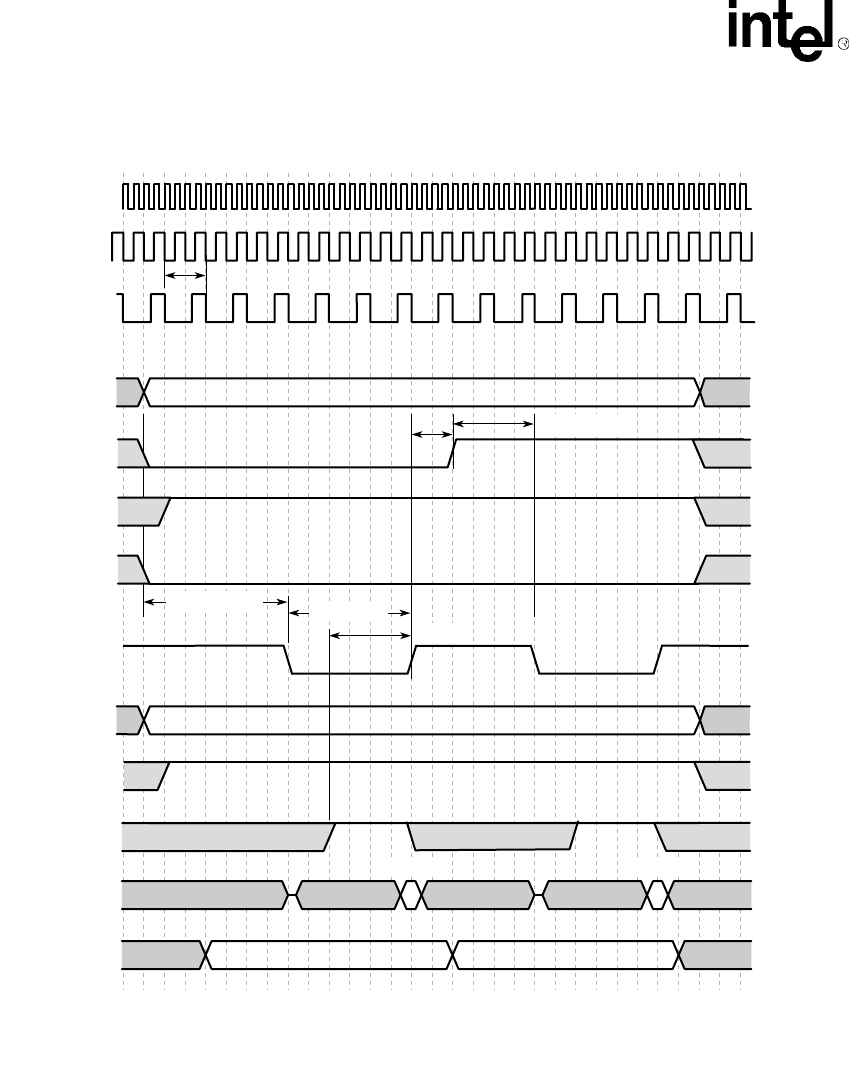

Figure 10-23. PC-Card I/O 16-Bit Access to 8-Bit Device

Timing parameters are in memory clock cycle units. All are minimums except as noted:

Address access time:

6*(BS_xx+1) + 1 half-word or first byte FAST=0

5*(BS_xx+1) second byte FAST=0

4*(BS_xx+1) + 1 half-word or first byte FAST=1

4*(BS_xx+1) second byte FAST=1

Command (nPOE, nPWE, nPIOR, nPIOW) assertion time: 3*(BS_xx+1)

Address setup to command assert:

3*(BS_xx+1) + 1 half-word or first byte FAST=0

A6653-02

CPU

Clock

Memory

Clock

PSKTSEL

A(25:1),

nPREG

BCLK

nPCE1

nPIOR,

nPIOW

RD/nWR

nOIS16

A(0)

nPEC2

3

*

(BS_xx+1)+1

3

*

(BS_xx+1)

BS_xx+3

Low Byte High Byte

BS_xx+1

2

*

(BS_xx+1)

Low Byte High Byte

* Contents of PC Card register fields:

MECR:BS_xxn=1 MECR:FASTn=0

Read Data

(7:0)

Write Data

(7:0)

nPWAIT

BS_xx+1