SA-1110 Developer’s Manual 123

Memory and PC-Card Control Module

10.1.3 Writes

The write buffer and DMA requests can generate single (nonburst) accesses that each write one

byte, one halfword, or one full word. They also can generate burst accesses that each write one,

two, three, or four full words. Additionally, cache line castouts can cause the write buffer to

generate burst accesses that each write eight full words.

For stores to DRAM or SRAM memory spaces, the nCAS[3:0] lines enable the corresponding byte

of the data bus during a write transaction. Flash memory space stores must be the width of the

Flash data bus, either 16 or 32 bits.

10.1.4 Transaction Summary

Table 10-2 lists all the transactions that the SA-1110 can generate. No burst will cross an aligned

32-byte boundary. Note that on a 16-bit data bus, each full word access becomes a two half-word

burst, with address bit 1 always starting at 0. Each write access to Flash memory space must take

place in one nonburst operation, regardless of bus size.

10.1.5 Read-Lock-Write

The read-lock-write sequence is generated by an SWP(SWAP) instruction to a

noncacheable/nonbufferable location. Locked access to memory is ensured through internal

arbitration of accesses to the memory controller. On the external memory bus it appears as a single

read followed by a single write.

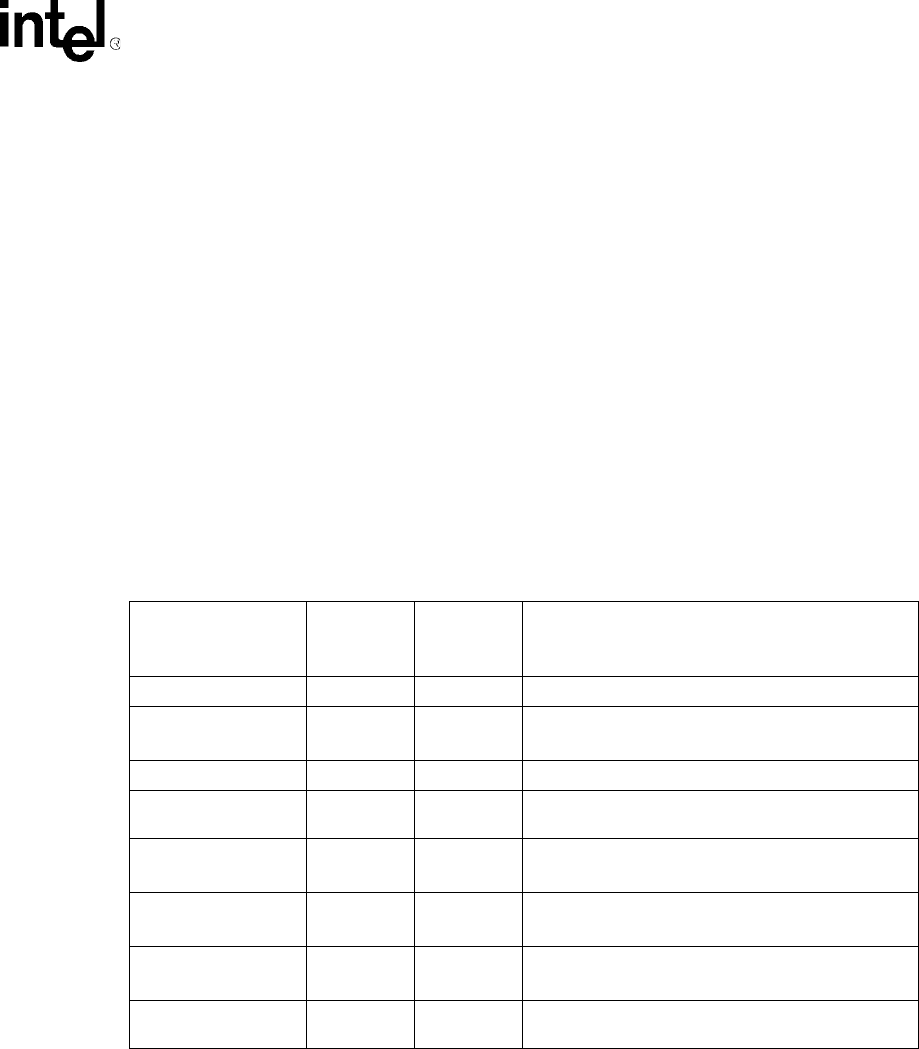

Table 10-2. SA-1110 Transactions On 32-Bit Data Buses

Bus Operation

Burst

Size

(Words)

Starting

Address

Bits[4:2]

Description

Read single 1 Any Generated by core, DMA, or read buffer request.

Read burst

4

0

4

Generated by read buffer or DMA request.

Read burst 8 0 Generated by cacheline fills or read buffer request.

Write single

1Any

1..4 bytes are written as specified by the byte mask.

Generated by write buffer or DMA request.

Write burst

2

0, 1, 2

4, 5, 6

All 4 bytes of each word are written. Generated by

write buffer or DMA request.

Write burst

3

0, 1

4, 5

All 4 bytes of each word are written. Generated by

write buffer or DMA request.

Write burst

4

0

4

All 4 bytes of each word are written. Generated by

write buffer or DMA request.

Write burst

80

Cacheline copyback. All 32 bytes are written.

Generated by write buffer.