SA-1110 Developer’s Manual 407

Package and Pinout

Note: All VDDX1, VDDX2,andVDDX3 pins should be connected directly to the VDDX power plane

of the system board. VDDP should be connected directly to the VDD plane of the system board.

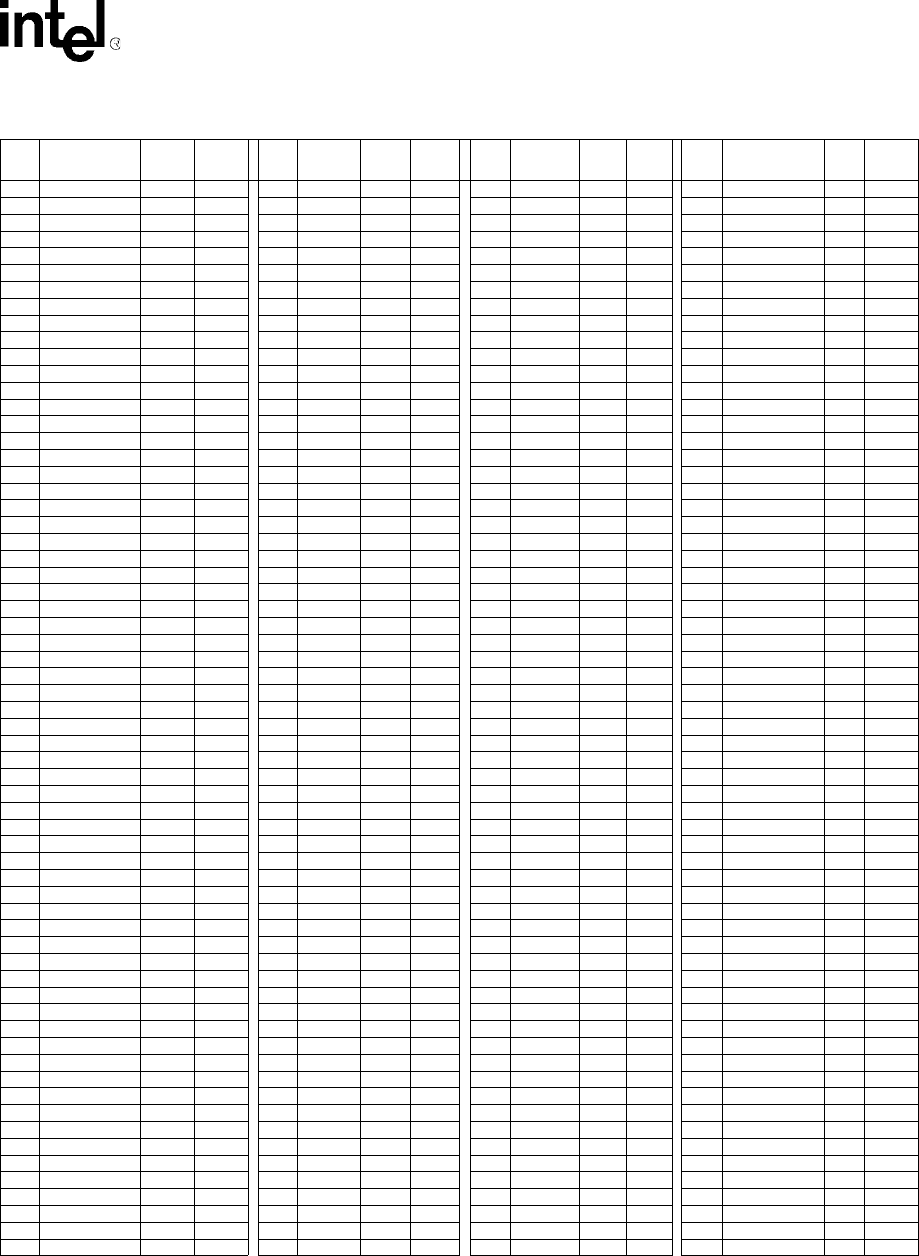

Table 14-1. SA-1110 Pinout – Numeric Signal Pin List

Pin Signal Type

BGA

Pad

Pin Signal Type

BGA

Pad

Pin Signal Type

BGA

Pad

Pin Signal Type

BGA

Pad

1RXD_C I/O B1 65VDDX1 D5 129 nSDRAS O M14 193 RXD_2 I/O B10

2TXD_C I/OC2 66VSSX F7 130 nSDCAS O L16 194 TXD_2 I/O D10

3 VDDX2 E12 67 GP 21 I/O T3 131 nRAS 3 O L15 195 RXD_3 I/O C10

4 VSSX A1 68 GP 20 I/O R4 132 nRAS 2 O L14 196 TXD_3 I/O A10

5 VDD C1 69 GP 19 I/O T4 133 nRAS 1 O L13 197 VSSX H9

6 VSS D3 70 GP 18 I/O P5 134 nRAS 0 O K16 198 VDDX1 E10

7 D 0 I/O E4 71 GP 17 I/O R5 135 nCAS 3 O K13 199 VSS A9

8 D 8 I/O D2 72 GP 16 I/O T5 136 nCAS 2 O K15 200 TXTAL I B9

9 D 16 I/O D1 73 GP 15 I/O N6 137 VSSX G8 201 TEXTAL O C9

10 D 24 I/O E3 74 GP 14 I/O P6 138 VDDX2 K5 202 PEXTAL I A8

11 D 1 I/O F4 75 VDDX1 D9 139 VSS K14 203 PXTAL O B8

12 D 9 I/O E2 76 VSSX F8 140 VDD J16 204 VDDP C8

13 D 17 I/O E1 77 GP 13 I/O R6 141 nCAS 1 O J15 205 VSS D8

14 D 25 I/O F3 78 GP 12 I/O R7 142 nCAS 0 O J14 206 VDD A7

15 VDDX2 F12 79 GP 11 I/O T6 143 RD_nWR O J13 207 nRESET I B7

16 VSSX B2 80 GP 10 I/O P7 144 RDY I H13 208 nRESET_OUT O C7

17 D 2 I/O F2 81 GP 9 I/O T7 145 nCS 5 O H16 209 VDDX3 D7

18 D 10 I/O F1 82 GP 8 I/O P8 146 nCS 4 O H15 210 ROMSEL I D6

19 D 18 I/O G4 83 GP 7 I/O N8 147 nCS 3 O H14 211 TCK_BYP I A6

20 D 26 I/O G3 84 GP 6 I/O R8 148 nCS 2 O G16 212 TESTCLK I B6

21 D 3 I/O G2 85 VDDX1 D11 149 VSSX G9 213 TMS I C6

22 D 11 I/O H6 86 VSSX F9 150 VDDX2 K12 214 TCK I C5

23 D 19 I/O G1 87 VDD T8 151 nCS 1 O G15 215 TDI I A5

24 D 27 I/O H4 88 VSS R9 152 nCS 0 O G14 216 TDO O B5

25 VDD H3 89 GP 5 I/O P9 153 A 25 O F16 217 nTRST I B4

26 VSS H2 90 GP 4 I/O T9 154 A 24 O G13 218 BATT_FAULT I A4

27 VDDX2 G5 91 GP 3 I/O N10 155 A 23 O F13 219 VSSX H10

28 VSSX C3 92 GP 2 I/O R10 156 A 22 O F15 220 VDDX1 E11

29 D 4 I/O H1 93 GP 1 I/O P10 157 A 21 O E16 221 VDD_FAULT I C4

30 D 12 I/O J6 94 GP 0 I/O T10 158 A 20 O F14 222 PWR_EN O A3

31 D 20 I/O J2 95 L_BIAS I/O R11 159 VSSX G10 223 SFRM_C O B3

32 D 28 I/O J3 96 L_PCLK I/O P11 160 VDDX2 L5 224 SCLK_C O A2

33 D 5 I/O J4 97 VDDX1 E6 161 A 19 O E15 VDDX1 K10

34 D 13 I/O J1 98 VSSX F10 162 A 18 O D16 VDDX1 K11

35 D 21 I/O K2 99 LDD0 I/O N12 163 A 17 O E14 VDDX1 L10

36 D 29 I/O K3 100 LDD1 I/O T11 164 A 16 O D15 VDDX1 L11

37 VDDX2 G12 101 LDD2 I/O R12 165 A 15 O C16 VDDX1 M6

38 VSSX D4 102 LDD3 I/O P12 166 A 14 O E13 VDDX1 M7

39 D 6 I/O K1 103 LDD4 I/O T12 167 VSS D14 VDDX1 M8

40 D 14 I/O K4 104 LDD5 I/O R13 168 VDD C15 VDDX1 M9

41 D 22 I/O L3 105 LDD6 I/O T13 169 VSSX G11 VDDX1 M10

42 D 30 I/O L2 106 LDD7 I/O P13 170 VDDX2 L12 VDDX1 M11

43 D 7 I/O L1 107 VDDX1 E7 171 A 13 O D13 VDDX1 N7

44 D 15 I/O L4 108 VSSX F11 172 A 12 O B16 VDDX1 N9

45 D 23 I/O M2 109 L_LCLK I/O R14 173 A 11 O C14 VDDX1 N11

46 D 31 I/O M1 110 L_FCLK I/O T14 174 A 10 O B14 VDDX2 F5

47 VDDX2 H5 111 nPOE O R15 175 A 9 O B15 VDDX2 M5

48 VSSX E5 112 nPWE O T15 176 A 8 O A16 VDDX2 M12

49 SDCLK 2 O M3 113 nPIOR O T16 177 VSSX H7 VDDX2 N4

50 SDCKE 1 O N2 114 nPIOW O R16 178 VDDX1 E8 VDDX2 N5

51 SDCLK 1 O N3 115 VSSX G6 179 A 7 O A15 VSSX H11

52 SDCKE 0 O N1 116 VDDX2 J5 180 A 6 O A14 VSSX J7

53 SDCLK 0 O P1 117 VSS P14 181 A 5 O B13 VSSX J8

54 SMROM_EN I M4 118 VDD P15 182 A 4 O C13 VSSX J9

55 VDD P3 119 PSKTSL O P16 183 A 3 O A13 VSSX J10

56 VSS P2 120 nIOS16 I N13 184 A 2 O B12 VSSX J11

57 VDDX2 H12 121 nPWAIT I N16 185 A 1 O C12 VSSX K6

58 VSSX F6 122 nPREG O N14 186 A 0 O D12 VSSX K7

59 GP 27 I/O R1 123 nPCE2 O N15 187 VSSX H8 VSSX K8

60 GP 26 I/O T1 124 nPCE1 O M16 188 VDDX1 E9 VSSX K9

61 GP 25 I/O R2 125 nWE O M13 189 UDC- I/O A12 VSSX L6

62 GP 24 I/O P4 126 nOE O M15 190 UDC+ I/O C11 VSSX L7

63 GP 23 I/O T2 127 VSSX G7 191 RXD_1 I/O B11 VSSX L8

64 GP 22 I/O R3 128 VDDX2 J12 192 TXD_1 I/O A11 VSSX L9