178 SA-1110 Developer’s Manual

Memory and PC-Card Control Module

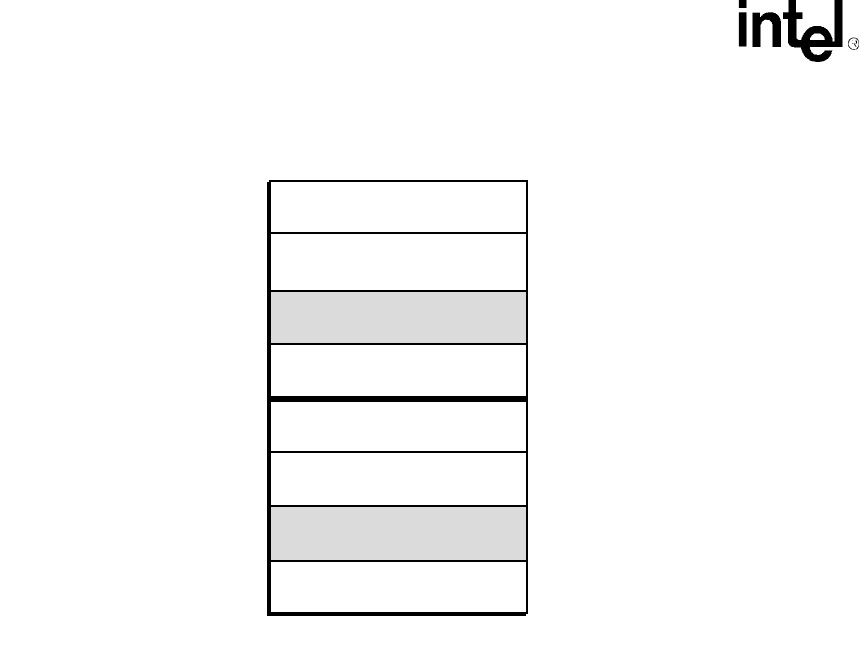

Figure 10-19. PC-Card Memory Map

The PC-Card memory space is divided into eight partitions, four for each card slot. The four

partitions for each card slot are common memory, I/O, attribute memory, and a reserved space.

Each partition starts on a 64 Mbyte boundary. Pins A[25:0], nPREG, and PSKTSEL are driven at

the same time. nPCE1 and nPCE2 are driven at address time for memory and attribute accesses.

For I/O accesses, the value of nPCE1 and nPCE2 depends on the value of nIOIS16 and thus will be

valid a finite time after nIOIS16 is valid.

Common memory and attribute accesses assert the nPOE or nPWE control signals. Memory and

attribute space is 16 bits wide by definition.

I/O accesses assert the nIOR or nIOW control signals and use the nIOIS16 input signal to deter-

mine the bus width of the transfer (8 or 16 bits). Transfers always start assuming a 16-bit bus. After

the address has been placed on the bus, an I/O device may respond by asserting nIOIS16 to indicate

that it can perform the transfer in a single 16-bit transfer. If nIOIS16 is not asserted within the

proper timeframe, the address is assumed to be to two 8-bit registers and the transfer is completed

as two consecutive 8-bit transfers on the low byte lane, D[7:0], with:

1) nPCE2 deasserted,

2) nPCE1 asserted,

3) A0 = 0 for the first 8-bit transfer, and

4) A0 = 1 for the second 8-bit transfer.

Note: The SA-1110 uses nPCE2 to indicate to the expansion device that the upper half of the data bus,

D[15:8], will be used for the transfer and nPCE1 to indicate that the lower half of the data bus,

D[7:0], will be used.

A6645-01

Socket 1 Memory Space

Socket 1 Attribute Space

Socket 0 Memory Space

Socket 0 Attribute Space

Socket 1 I/O Space

Socket 0 I/O Space

Reserved

Reserved

0h3C00 0000

0h3800 0000

0h3400 0000

0h3000 0000

0h2C00 0000

0h2800 0000

0h2400 0000

0h2000 0000