SA-1110 Developer’s Manual 217

Peripheral Control Module

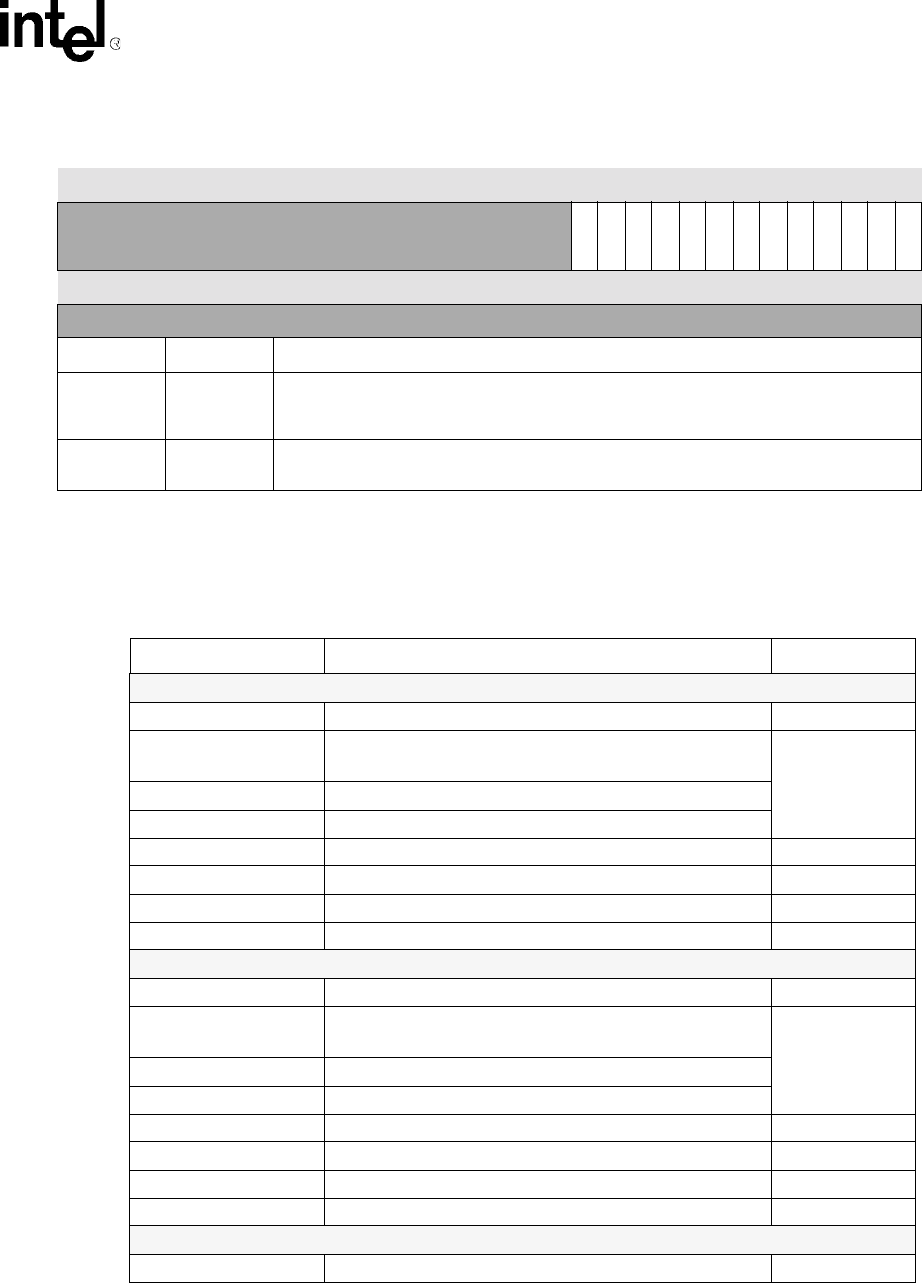

11.6.2 DMA Register List

The following table lists the registers contained within the DMA controller:

DBTBn Read/Write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

TCB 12

TCB 11

TCB 10

TCB 9

TCB 8

TCB 7

TCB 6

TCB 5

TCB 4

TCB 3

TCB 2

TCB 1

TCB 0

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 ? ? ? ? ? ? ? ? ? ? ? ? ?

Bits Name Description

12..0 TCB 12..0

Transfer count (buffer B).

This field is a 13-bit value and contains the current transfer count (in bytes) for the transfer to or

from buffer B. The maximum value programmed via this transfer count is 8191 bytes.

31..13 —

Reserved.

These bits are reserved and read as zeros. Writes to this field have no effect.

Physical Address Register Name Symbol

Channel 0 Registers

0h B000 0000 DMA device address register. DDAR0

0h B000 0004

DMA control/status register 0.

Write 0x7F to set.

DCSR0

0h B000 0008 Write 0x7F to clear.

0h B000 000C Read only.

0h B000 0010 DMA buffer A start address 0. DBSA0

0h B000 0014 DMA buffer A transfer count 0. DBTA0

0h B000 0018 DMA buffer B start address 0. DBSB0

0h B000 001C DMA buffer B transfer count 0. DBTB0

Channel 1 Registers

0h B000 0020 DMA device address register 1. DDAR1

0h B000 0024

DMA control/status register 1.

Write 0x7F to set.

DCSR1

0h B000 0028 Write 0x7F to clear.

0h B000 002C Read only.

0h B000 0030 DMA buffer A start address 1. DBSA1

0h B000 0034 DMA buffer A transfer count 1. DBTA1

0h B000 0038 DMA buffer B start address 1. DBSB1

0h B000 003C DMA buffer B transfer count 1. DBTB1

Channel 2 Registers

0h B000 0040 DMA device address register 2 DDAR2