90 SA-1110 Developer’s Manual

System Control Module

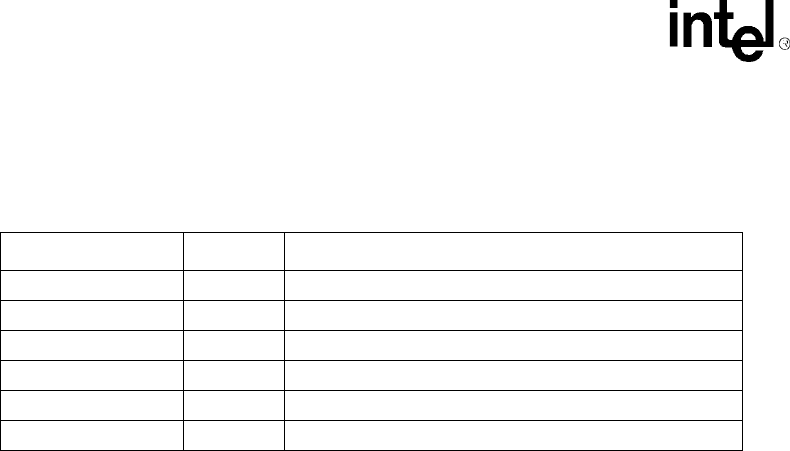

9.2.2 Interrupt Controller Register Locations

The following table shows the registers associated with the interrupt controller block and the

physical addresses used to access them.

9.3 Real-Time Clock

The SA-1110 contains a real-time clock (RTC) that provides a general-purpose real-time reference

for use by the system. The RTC is uninitialized after a hardware reset (nRESET) and must be

written by the user to the desired value. Thereafter, the counter will remain valid until another

hardware reset (assumed to be infrequent). The value of the counter is unaffected by transitions

into and out of sleep, idle, software reset, or a watchdog reset. The counter is incremented on rising

edges of the 1-Hz clock.

In addition to the counter [ RTC counter register (RCNR) ], the RTC incorporates a 32-bit alarm

register (RTAR). The RTAR may be programmed with a value to be compared against the counter.

RCNR is incremented on each rising edge of the 1-Hz clock. Throughout each 1-Hz clock period

RCNR is compared to RTAR. If the values match and the alarm interrupt is enabled, then a status

bit is set. This status bit is also routed to the interrupt controller and may be programmed to

generate a CPU interrupt.

Another status bit is available that is set whenever the 1 Hz clock interrupt occurs. Each status bit

may be cleared by writing a one to the status register in the desired bit position. The 1-Hz clock is

generated by dividing down the 32.768-kHz crystal oscillator output. This divider logic is

programmable to allow the user to “trim” the counter to adjust for inherent inaccuracies in the

crystal’s frequency. This trimming mechanism permits the user to adjust the RTC to an accuracy of

+/- 5 seconds per month. The trimming procedure is described later in this section.

Note: The 32.768 kHz crystal may take 2-10 seconds to stabilize after a hardware reset. The Power

Manager Oscillator Status Register (0x9002001c) bit Oscillator OK (bit 0) is set when the 32.768

kHz clock has stabilized after a hardware reset.

9.3.1 RTC Counter Register (RCNR)

The RTC counter register (RCNR) is a read/write register and is not cleared by any reset source.

The counter may be written by the processor at any time although it is recommended that the

operating system prevent inadvertent writes to the RCNR through the use of the MMU protection

mechanisms.

Address Name Description

0h 9005 0000 ICIP Interrupt controller IRQ pending register

0h 9005 0004 ICMR Interrupt controller mask register

0h 9005 0008 ICLR Interrupt controller level register

0h 9005 0010 ICFP Interrupt controller FIQ pending register

0h 9005 0020 ICPR Interrupt controller pending register

0h 9005 000C ICCR Interrupt controller control register