SA-1110 Developer’s Manual 335

Peripheral Control Module

functionality of the UART module or wait for a 0 to 1 transition and then a 1 to 0 transition of TBY

to ensure that the data is transmitted.

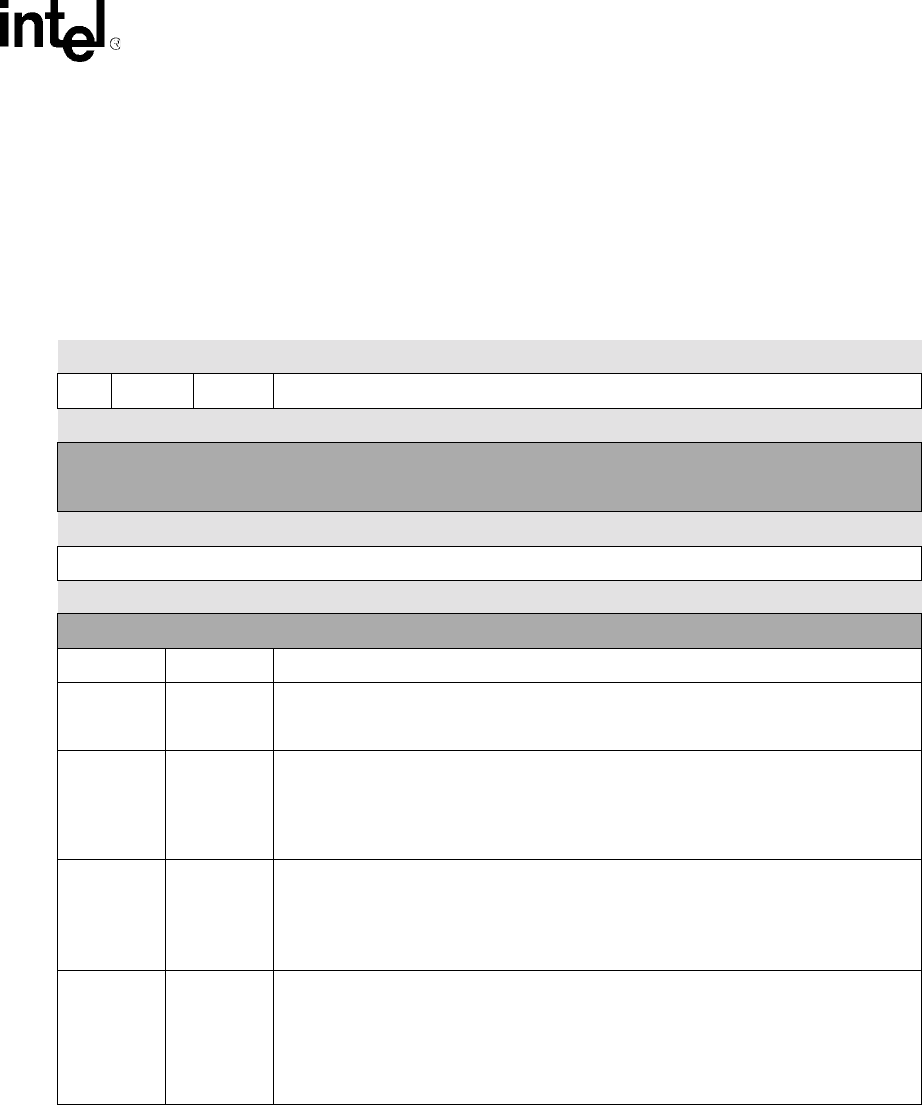

The following table shows the bit locations corresponding to the data field, parity, framing, and

receiver overrun error bits within the UART data register. Note that both FIFOs are cleared when

the SA-1110 is reset, the transmit FIFO is cleared when writing TXE=0, and the receive FIFO is

cleared when writing RXE=0.

11.11.7 UART Status Register 0

UART status register 0 (UTSR0) contains bits that signal the transmit FIFO interrupt request,

receive FIFO interrupt request, receiver idle detect, the begin and end of receiver break detect

conditions, and the error in receive FIFO condition. Each of these hardware-detected events signals

an interrupt request to the interrupt controller.

0h 8005 0014 UTDR Read/Write

10 9 8 7 6 5 4 3 2 1 0

ROR FRE

PRE Bottom of Receive FIFO Data

Reset

? ? ? ? ? ? ? ? ? ? ?

Read Access

Note: ROR, FRE, PRE are not read, but rather are transferred to corresponding status bits in UTSR1 each time a

data value is transferred to UTDR.

7 6 5 4 3 2 1 0

Top of Transmit FIFO Data

Reset

? ? ? ? ? ? ? ?

Write Access

Bits Name Description

7..0 DATA

Top/bottom of transmit/receive FIFO data.

Read – Bottom of receive FIFO data.

Write – Top of transmit FIFO data.

8PRE

Parity error.

0 – No parity errors encountered in the receipt of this data (or parity disabled).

1 – Parity error encountered in the receipt of this data.

Note: Each time an 11-bit value reaches the bottom of the receive FIFO, bit 8 from the last

FIFO entry is transferred to the PRE bit in UTSR1.

9FRE

Framing error.

0 – Stop bit for this frame was a one.

1 – Stop bit for this frame was a zero.

Note: Each time an 11-bit value reaches the bottom of the receive FIFO, bit 9 from the last

FIFO entry is transferred to the FRE bit in UTSR1.

10 ROR

Receiver overrun.

0 – No receiver overrun has been detected.

1 – Receive logic attempted to place data into receive FIFO while it was full; one or more

data values following this entry were lost.

Note: Each time an 11-bit value reaches the bottom of the receive FIFO, bit 10 from the

last FIFO entry is transferred to the ROR bit in UTSR1.