SA-1110 Developer’s Manual 55

Coprocessors 6

The operation and configuration of the Intel

®

StrongARM

*

SA-1110 Microprocessor (SA-1110) is

controlled with coprocessor instructions, configuration pins, and memory-management page

tables. The coprocessor 15 instructions manipulate on-chip registers that control the configuration

of the cache, write buffer, MMU, read buffer, breakpoints, and other configuration options.

Note: The gray areas in the register and translation diagrams are reserved and should be programmed 0

for future compatibility.

6.1 Internal Coprocessor Instructions

The on-chip cache, MMU, write buffer, and read buffers are controlled using MRC instructions and

MCR instructions. These operations to coprocessor 15 are allowed only in nonuser modes except

when read-buffer operations are explicitly enabled. The undefined instruction trap is taken if

accesses are attempted in user mode. Figure 6-1 shows the format of internal coprocessor

instructions MRC and MCR.

Note: The write buffer must be flushed prior to loading the read buffer to maintain coherency between the

two buffers. But, if user-mode MCR access is enabled for the read buffer and the flush is attempted

while in user mode, an undefined instruction exception will occur. In this case, the exception

handler must perform the write buffer flush, then return to user mode to execute the read buffer

load. Alternatively, an SWI instruction can be used as a service call to flush the write buffer."

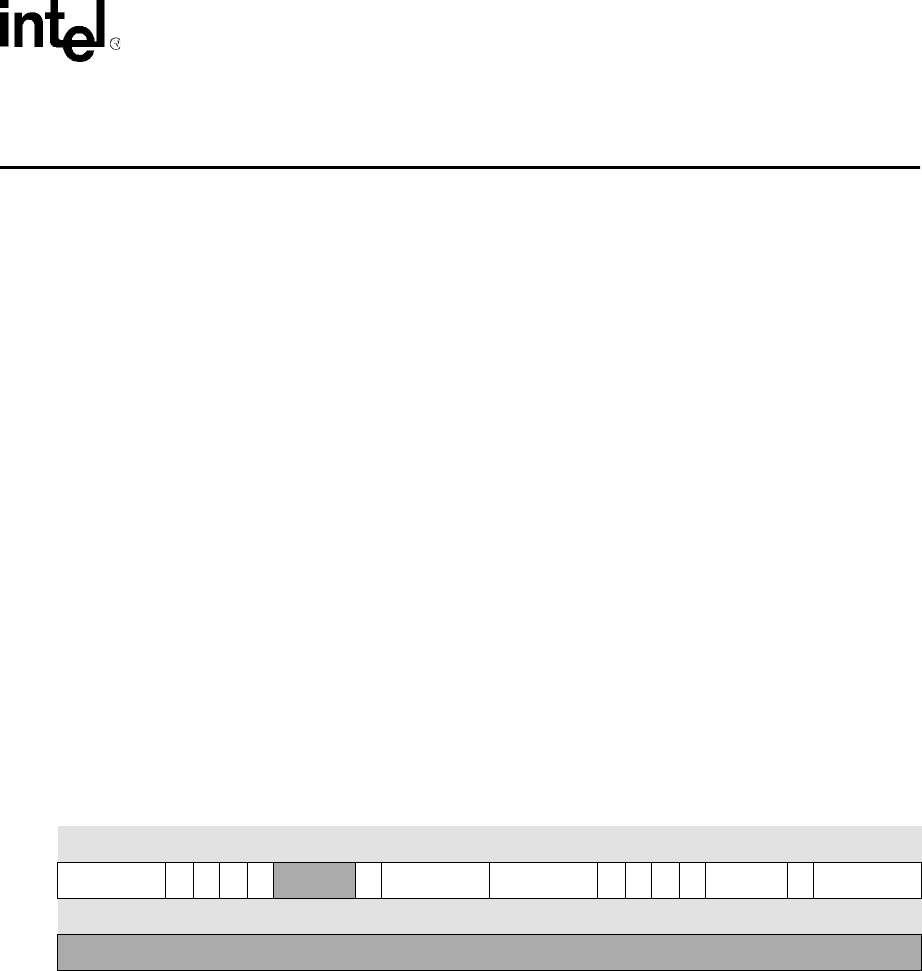

Figure 6-1. Format of Internal Coprocessor Instructions MRC and MCR

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Cond 1110

n CRn Rd 1

111

OPC_2

1 CRm

Cond ARM

*

condition codes

n 1 MRC register read

0MCRregisterwrite

CRn SA-1110 register

Rd ARM register

OPC_2 Function bits for some MRC/MCR instructions

CRm Function bits for some MRC/MCR instructions