284 SA-1110 Developer’s Manual

Peripheral Control Module

11.8.6 UDC IN Maximum Packet Register (UDCIMP)

UDCIMP holds the value of the “maximum packet size minus one” that the SA-1110 UDC will

transmit to the HOST (Bulk IN). “Maximum packet size minus one” is used to accommodate a

maximum Data Packet size of 256 bytes, without needing a maximum packet size field of more

than 8-bits. To allow the SA-1110 UDC to provide a 256-byte (or less) Data Packet to the HOST, a

value of 0xff (255) should be written to UDCIMP. After reset of the SA-1110 UDC, UDCIMP

contains 0x08, allowing the SA-1110 UDC to transmit a 9-byte (or less) Data Packet to the Host.

The SA-1110 UDC will not transmit a 0-byte Data Packet from Endpoint 2.

Note: A bulk transfer typically consists of some number of full-size 64-byte packets and is terminated by

a packet less than the full size. However, if the amount of data transferred is an exact multiple of

64-bytes, then a terminating packet of 0-bytes of data (plus header and checksum) is needed. The

SA-1110 UDC does not allow a 0-byte packet to be transmitted, so the device driver is forced to

substitute a 1-byte packet and the Host receives more data than it expects. Protocol support is

needed so that the appropriate Host-side device driver can allow buffer space for the extra byte,

detect when it gets sent, and discard it. Consequently, certain standard USB class protocols cannot

be implemented using the SA-1110 UDC; therefore, custom Host-side device drivers will generally

have to be provided, rather than re-using existing ones that implement the standard protocol.

Note: Due to the internal synchronization required by the SA-1110 UDC configuration registers, it is

possible for the CPU to write to the SA-1110 UDC registers and FIFOs too fast. So, a single write

to the SA-1110 UDC must be completed before another write may take place. To ensure that a

single write is completed, it is necessary to observe the effect of the write before another write may

take place. This can be accomplished by writing to a SA-1110 UDC register and then reading back

the same register two times. The second read-back should produce correct data.

11.8.7 UDC Endpoint 0 Control/Status Register (UDCCS0)

UDCCS0 contains 8 bits that are used to operate Endpoint 0.

Note: Due to the internal synchronization required by the SA-1110 UDC configuration registers, it is

possible for the CPU to write to the SA-1110 UDC registers and FIFOs too fast. So, a single write

to the SA-1110 UDC must be completed before another write may take place. To ensure that a

single write is completed, it is necessary to observe the effect of the write before another write may

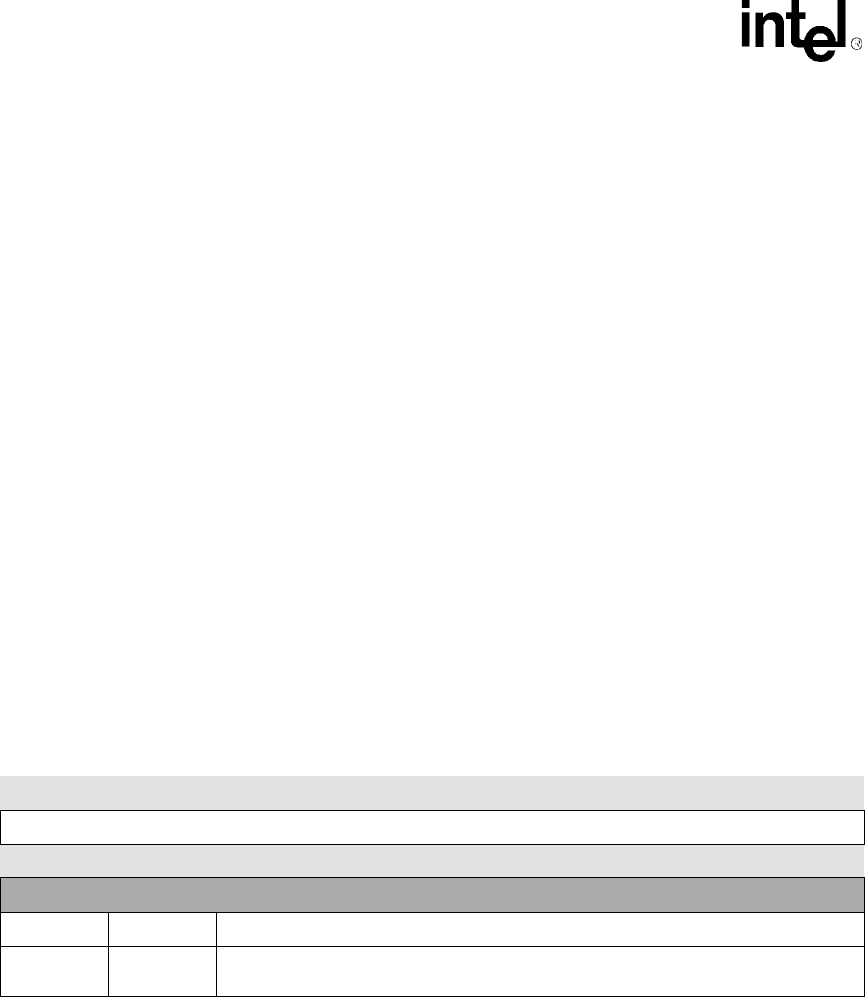

0h 8000 000C UDCIMP Read/Write

7 6 5 4 3 2 1 0

Maximum Packet Size - 1

Reset

0 0 0 0 1 0 0 0

Bits Name Description

7..0 IN MaxP

IN Maximum packet size.

8-bit field containing the value of the number of bytes to transmit minus one.