62 SA-1110 Developer’s Manual

Coprocessors

6.2.13 Register 14 – Debug Support (Breakpoints)

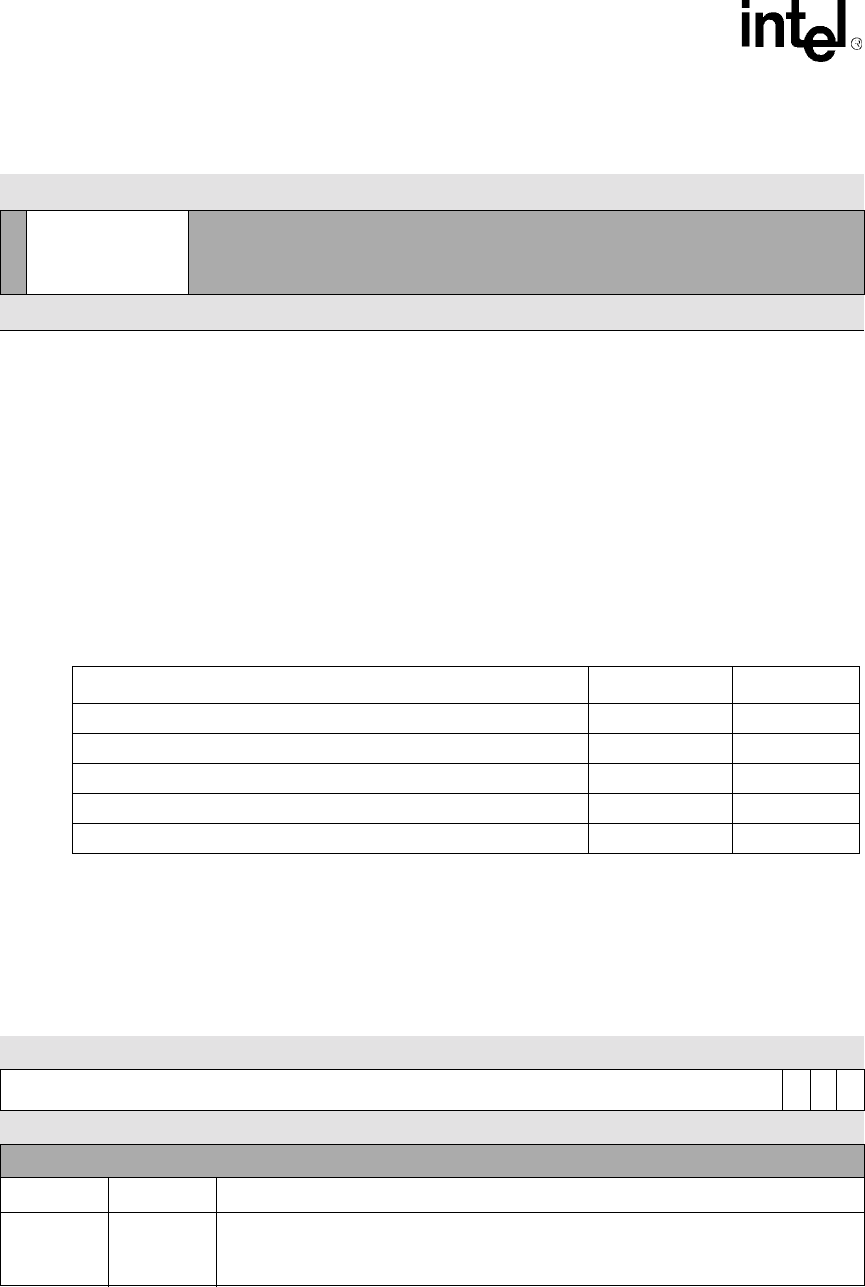

The SA-1110 supports address and data breakpoints through register 14 of coprocessor 15. The

instruction formats follow. For a description of the breakpoint operation, see Chapter 15, “Debug

Support”. The following table shows the OPC_2 and CRm field encodings used to access the

address and data breakpoints.

The DBAR, DBVR, DBMR and DBCR registers are Read/Write registers. The IBCR is a

Write-Only register.

The DBCR register is a 3-bit register used to control the enabling and disabling of the data

breakpoints. Bits 0..2 are valid and positioned as shown below. Bits 3..31 are reserved. These bits

read as zeros and writes have no effect.

Register 13 – Process ID Read/Write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

Process ID

Reserved

Function OPC_2 CRm

Access data breakpoint address register (DBAR). 0b000 0b0000

Access data breakpoint value register (DBVR). 0b000 0b0001

Access data breakpoint mask register (DBMR). 0b000 0b0010

Load data breakpoint control register (DBCR). 0b000 0b0011

Write instruction breakpoint address and control register (IBCR). 0b000 0b1000

Data Breakpoint Control Register

(DBCR)

Read/Write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

sdw

saw

lw

Bits Name Description

0lw

Load watch

0 – Disable load watch

1 – Enable load watch