280 SA-1110 Developer’s Manual

Peripheral Control Module

11.8.3.1 UDC Disable (UDD)

The UDD bit is used to enable or disable the SA-1110 UDC. When the CPU writes a 0 to the UDD

bit, the SA-1110 UDC is enabled for serial transmission or reception; when the CPU writes a 1 to

the UDD bit, the SA-1110 UDC is disabled and the UDC+ and UDC- pins are tristated.

Writing a 1 to the UDD bit causes the entire SA-1110 UDC to be reset. If the SA-1110 UDC is

actively transmitting or receiving data when a 1 is written to the UDD bit, the SA-1110 UDC stops

immediately, bits remaining in the transmit or receive serial shifter are reset, and all entries within

the Transmit Data FIFO and Receive Data FIFO are reset.

An SA-1110 reset causes the UDD bit to be automatically set to 1, disabling the SA-1110 UDC.

This gives control of the SA-1110 UDC’s pins to the PPC unit, which configures pins as inputs.

11.8.3.2 UDC Active (UDA)

The read-only UDA bit can be read to determine if the SA-1110 UDC is currently active. Reading a

1 indicates the SA-1110 UDC is currently involved in a transaction.

11.8.3.3 Resume Interrupt Mask (RESIM)

The RESIM bit masks or enables the resume interrupt request.

2RESIM

Resume interrupt mask.

0 – Resume interrupt enabled..

1 – Resume interrupt disabled.

3EIM

Endpoint 0 interrupt mask.

0 – Endpoint 0 interrupt enabled.

1 – Endpoint 0 interrupt disabled.

4RIM

Receive interrupt mask.

0 – Receive interrupt enabled.

1 – Receive interrupt disabled.

5TIM

Transmit interrupt mask.

0 – Transmit interrupt enabled.

1 – Transmit interrupt disabled.

6SUSIM

Suspend interrupt mask.

0 – Suspend interrupt enabled.

1 – Suspend interrupt disabled.

7 Reserved/B5

Reserved in A0, B0, B1, B2, and B4 versions of the SA-1110. For the B5 version of the

SA-1110, setting this bit to 1 activates the internal fix for Errata 29.

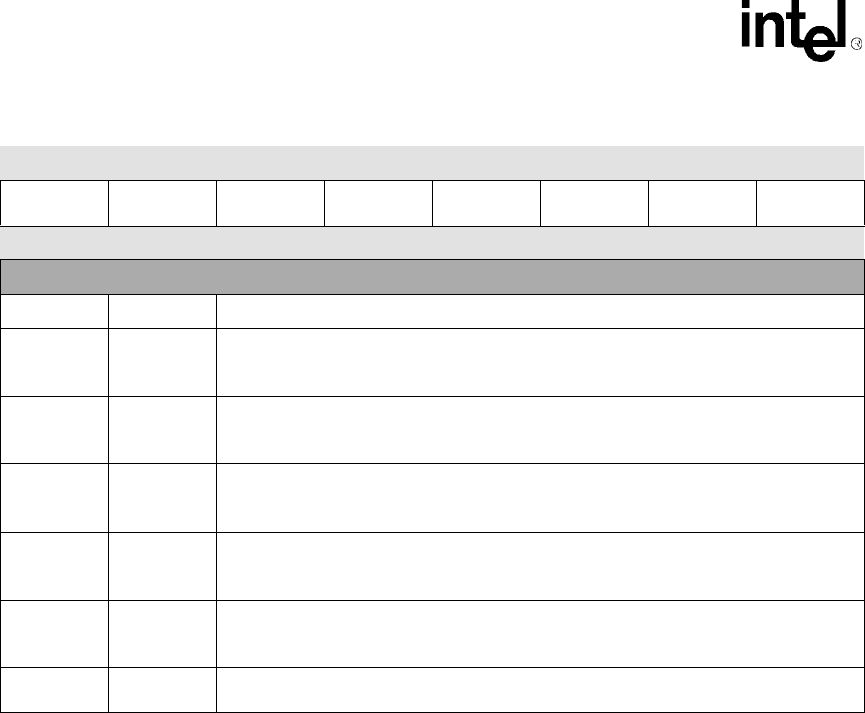

0h 8000 0000 UDCCR Read/Write and Read-Only

7 6 5 4 3 2 1 0

Reserved/B

5

SUSIM TIM RIM EIM RESIM UDA

UDD

Reset

0 1 0 0 0 0 0 1

Bits Name Description