SA-1110 Developer’s Manual 313

Peripheral Control Module

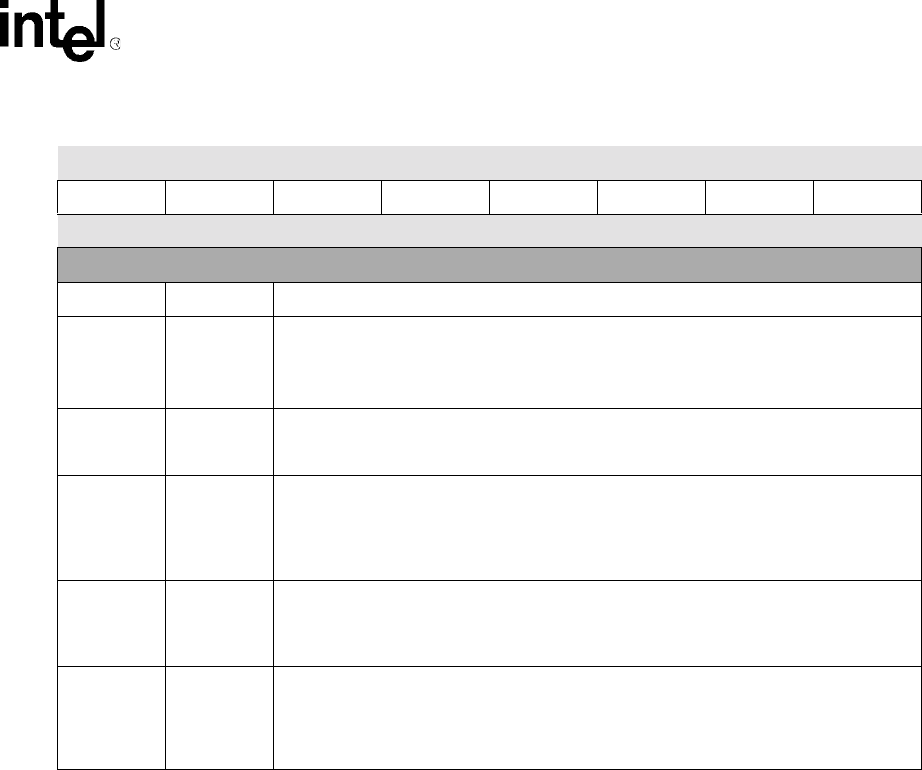

11.10.7 HSSP Control Register 1

HSSP control register 1 (HSCR1) contains the 8-bit address match value field that is used by the

HSSP to selectively receive frames.

Note: A question mark (?) signifies that the Reset value of that bit is undefined when the processor has

completed its reset cycle.

11.10.7.1 Address Match Value (AMV)

The 8-bit address match value (AMV) field is programmed with an address value that is used to

selectively store only the data within receive frames that have the same address value. The address

match enable (AME) bit must be set to enable this function. For incoming frames, which have the

same address value as the AMV field, the frame’s address, control, and data are stored in the

receive FIFO. For those that do not, the remainder of the frame is ignored and the receive logic

switches to hunt mode, looking for the preamble in the incoming data stream. One special address

exists, which is always matched by the address match logic regardless of the value programmed in

AMV. When address matching is enabled, whenever a frame is received with an address containing

all ones (11111111), the value programmed in AMV is ignored and the frame data is automatically

3TXE

Transmit enable.

0 – HSSP transmit logic disabled; control of the TXD2 pin is given to the PPC unit if ITR=1.

1 – HSSP transmit logic enabled if ITR=1.

Note: A SIP is transmitted immediately after the transmitter is enabled (TXE = 0 → 1).

4RXE

Receive enable.

0 – HSSP receive logic disabled; control of the RXD2 pin is given to the PPC unit if ITR =1.

1 – HSSP receive logic enabled if ITR=1.

5RIE

Receive FIFO interrupt enable.

0 – Receive FIFO two- or three-fifths full or more condition does not generate an interrupt

(RFS bit ignored).

1 – Receive FIFO two- or three-fifths full or more condition generates an interrupt (state of

RFS sent to interrupt controller).

6TIE

Transmit FIFO interrupt enable.

0 – Transmit FIFO half-full or less condition does not generate an interrupt (TFS bit ignored).

1 – Transmit FIFO half-full or less condition generates an interrupt (state of TFS sent to

interrupt controller).

7AME

Address match enable.

0 – Disable receiver address match function, store data from all incoming frames in receive

FIFO.

1 – Enable receiver address match function; do not FIFO data unless address recognized

or incoming address contains all ones (0hFF).

0h 8004 0060 HSCR0 Read/Write

7 6 5 4 3 2 1 0

AME TIE RIE RXE TXE TUS LBM

ITR

Reset

? ? ? 0 0 ? ? ?

(Sheet 2 of 2)

Bits Name Description