SA-1110 Developer’s Manual 441

Internal Test

Internal Test D

The Test Unit contains a register that enables certain test modes. Some of these test modes are

reserved for manufacturing test and should not be invoked by an end-user.

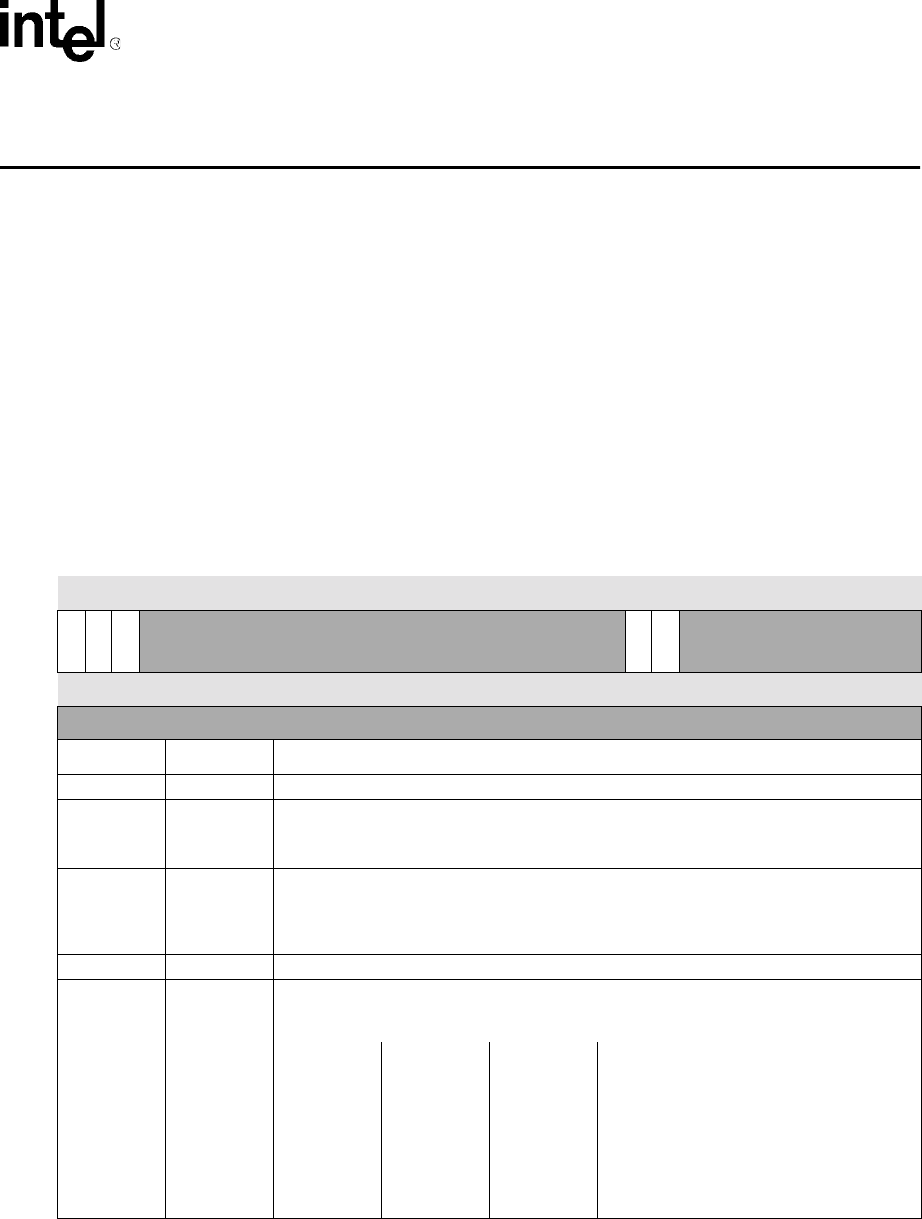

D.1 Test Unit Control Register (TUCR)

The Test Unit Control Register (TUCR) contains control bits that put the Intel

®

StrongARM

*

SA-1110 Microprocessor (SA-1110) in various test modes. It is recommended that the operating

system write protect these registers under normal conditions to prevent them from being

inadvertently written. The following figure shows the format of this register. At reset reserved bits

are zero. Writing reserved bits to one can lead to unpredictable results.

Test Unit Control Register: TUCR

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TSEL2

TSEL1

TSEL0

Reserved

MR

PMD

Reserved

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

8..0 — Reserved.

9PMD

Power management disable.

When PMD is set, sleep mode is disabled and the SA-1110 ignores the ForceSleep bit, as

well as the BATT_FAULT and VDD_Fault pins. This bit is cleared on hard reset.

10 MR

Memory request mode. Controls two GPIO pins used for external arbitration and for the

memory bus.

0 – GP 21 and GP 22 are not used for an alternate function.

1 – GP 21 and GP 22 are reserved for use as MBGNT and MBREQ, respectively.

28..11 — Reserved.

31..29 TSEL2..0

Test selects. Routes internal signals out onto GPIO 27 for observing internal clock signals.

To observe these clocks, set bit 27 to one in the GAFR and GPDR registers and set the

TSEL bits to the following settings to select which clock is driven onto GP 27:

TSEL2

0

0

0

0

1

1

1

1

TSEL1

0

0

1

1

0

0

1

1

TSEL0

0

1

0

1

0

1

0

1

GP 27(alternate function)

32-kHz oscillator

3.6864-MHz oscillator

VDD ring oscillator/16

96-MHz PLL/4

32-kHz oscillator (also enable rclk on GP 26)

3.6864-MHz oscillator

Main PLL/16

VDDL ring oscillator/4