360 SA-1110 Developer’s Manual

Peripheral Control Module

11.12.6 MCP Status Register

The MCP status register (MCSR) contains bits that signal FIFO overrun and underrun errors, and

FIFO service requests. Each of these conditions signal an interrupt request to the interrupt

controller. The status register also flags when transmit FIFOs are not full, when the receive FIFOs

are not empty, when a codec control register read or write is complete, and when the audio or

telecom portion of the codec is enabled (no interrupt generated).

A bit that can cause an interrupt signals the interrupt request as long as the bit is set. Once the bit is

cleared, the interrupt is cleared. Read/write bits are called status bits; read-only bits are called flags.

Status bits are referred to as “sticky” (once set by hardware, must be cleared by software). Writing

a one to a sticky status bit clears it; writing a zero has no effect. Read-only flags are set and cleared

by hardware; writes have no effect. Additionally, some bits that cause interrupts have

corresponding mask/enable bits in the control register and are indicated in the following section

headings. Note that the user has the ability to mask all MCP interrupts by clearing bit 18 within the

interrupt controller mask register (ICMR). See the Section 9.2, “Interrupt Controller” on

page 9-83.

11.12.6.1 Audio Transmit FIFO Service Request Flag (ATS) (read-only,

maskable interrupt)

The audio transmit FIFO service request flag (ATS) is a read-only bit that is set when the audio

transmit FIFO is nearly empty and requires service to prevent an underrun. ATS is set any time the

audio transmit FIFO has four or fewer entries of valid data (half-full or less), and is cleared when it

has five or more entries of valid data. When the ATS bit is set, an interrupt request is made unless

the audio transmit FIFO interrupt request mask (ATE) bit is cleared. The state of ATS is also sent to

the DMA controller, and can be used to signal a DMA service request. Note that ATE has no effect

on the generation of the DMA service request. After the DMA or CPU fills the FIFO such that four

or more locations are filled within the audio transmit FIFO, the ATS flag (and the service request

and/or interrupt) is automatically cleared.

11.12.6.2 Audio Receive FIFO Service Request Flag (ARS) (read-only, maskable

interrupt)

The audio receive FIFO service request flag (ARS) is a read-only bit that is set when the audio

receive FIFO is nearly filled and requires service to prevent an overrun. ARS is set whenever the

audio receive FIFO has four or more entries of valid data (half-full or more), and is cleared when it

has three or fewer (less than half-full) entries of data. When the ARS bit is set, an interrupt request

is made unless the audio receive FIFO interrupt request mask (ARE) bit is cleared. The state of

ARS is also sent to the DMA controller, and can be used to signal a DMA service request. Note that

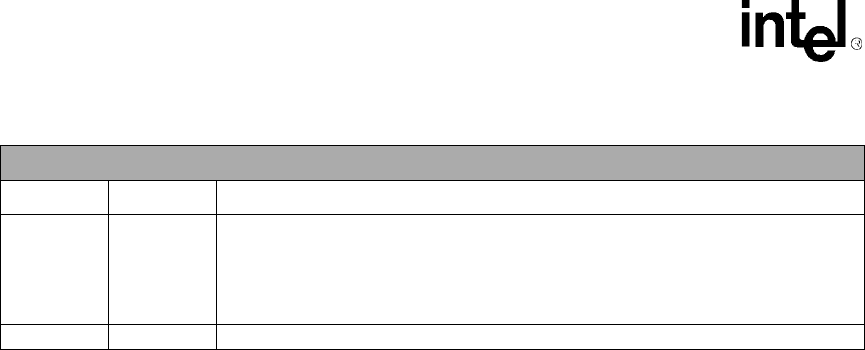

20..17

Codec

Register

Read/Write

Address

Codec register read/write address.

Read – If a codec write was last performed, contains address of previous register access;

next frame contains the address of the write. If a codec read was last performed, contains

address of the register read.

Write – Used to address a register to perform a read or write.

31..21 — Reserved

(Sheet 2 of 2)

Bits Name Description