SA-1110 Developer’s Manual 381

Peripheral Control Module

11.12.13 MCP Register Locations

Table 11-20 shows the registers associated with the MCP and the physical addresses used to access them.

5RFS

Receive FIFO service request (read-only).

0 – Receive FIFO is less than half-full (three or fewer entries filled) or SSP disabled.

1 – Receive FIFO is half-full or more (four or more entries filled) and SSP operation is enabled,

DMA service request signalled, interrupt request signalled if not masked (if RIE=1).

6ROR

Receive FIFO overrun.

0 – Receive FIFO has not experienced an overrun.

1 – Receive logic attempted to place data into receive FIFO while it was full, request interrupt.

15..7 — Reserved.

0h 8007 0074 SSP Status Register: SSSR Read/Write and Read-Only

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

ROR

RFS

TFS

BSY

RNE TNF

Reserved

0 0 0 0 0 0 0 0 0 ? 0 0 0 0 1 0

(Sheet 2 of 2)

Bits Name Description

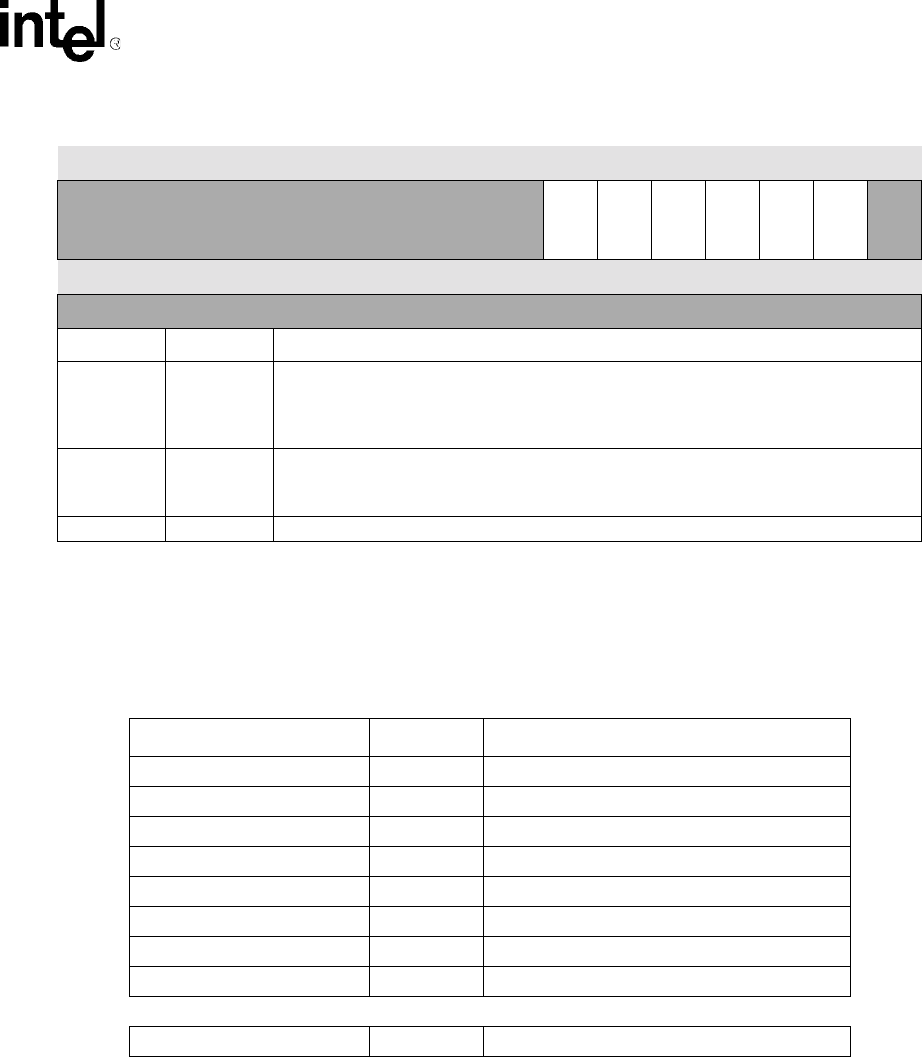

Table 11-20. MCP Control, Data, and Status Register Locations

Address Name Description

0h 8006 0000 MCCR0 MCP control register 0

0h 8006 0004 — Reserved

0h 8006 0008 MCDR0 MCP data register 0

0h 8006 000C MCDR1 MCP data register 1

0h 8006 0010 MCDR2 MCP data register 2

0h 8006 0014 — Reserved

0h 8006 0018 MCSR MCP status register

0h 8006 001C – 0h 8006 005C — Reserved

Note: MCCR1 resides within the same address space as the PPC.

0h 9006 0030 MCCR1 MCP control register 1