SA-1110 Developer’s Manual 297

Peripheral Control Module

Note: A question mark (?) signifies that the Reset value of that bit is undefined when the processor has

completed its reset cycle.

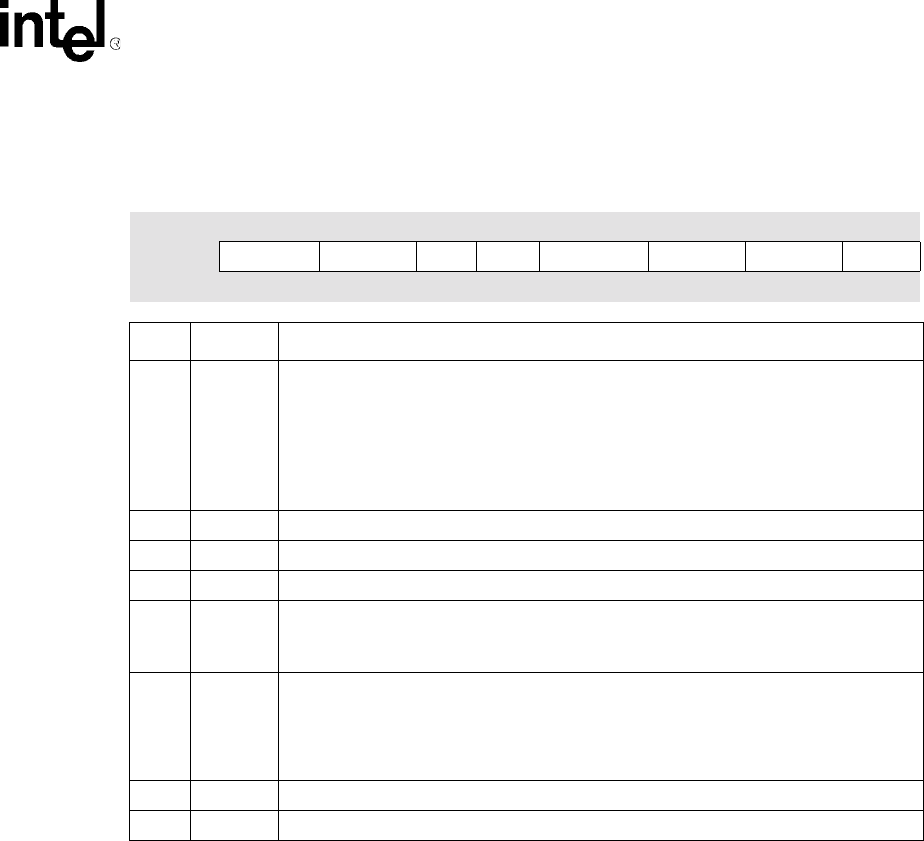

11.9.3 GPCLK Control Register 1

GPCLK Control Register 1 (GPCLKR1) contains one bit field that controls the general purpose

clock.

11.9.3.1 Transmit Enable (TXE)

The Transmit Enable bit enables and disables the GPCLK. When TXE=0, the GPCLK transmitter

logic is disabled. The clocks are turned off to save power.

When TXE=1, the GPCLK transmitter logic is enabled

Note: You must first program all other control bits before setting the TXE bit.

The following table shows the location of the TXE bit within GPCLK Control Register 1. The TXE

bit is reset to a known state to ensure the GPCLK is disabled following a reset of the SA-1110. All

other bits shown in the table are reserved for future use.

Address: 0h 8002 0060 GPCLKR0 Read/Write

Bit 7 6 5 4 3 2 1 0

Reserved Reserved SCD SCE Reserved Reserved Reserved SUS

Reset ? ? ? ? ? ? ? 0

Bit Name Description

0SUS

GPCLK/UART select.

0 – GPCLK mode selected.

1 – UART mode selected.

Note: For SUS=0, TXD1 and RXD1 control is given to the PPC unit. If UPR is set in

the PPC unit, SUS is ignored, the UART uses GPIO<14> to transmit and GPIO<15>

to receive data, and serial port 1 defaults to GPLCK mode. The user must also

program the GAFR and GPDR registers appropriately in the GPIO unit.

1 Reserved

Reserved for Future Expansion.

2 Reserved

Reserved for Future Expansion.

3 Reserved

Reserved for Future Expansion.

4SCE

Sample clock enable.

0 – Sample clock disabled.

1 – Sample clock enabled.

5SCD

Sample clock direction.

0 – If sample clock enabled, it is input on GPIO pin 16 and is not used.

1 – The sample clock which is generated within the GPCLK unit (the clock that is output

after dividing the 3.6864 MHz reference by the programmable BRD field), is output to the

GPIO pin 16 in the frequency range of 900 Hz – 3.6864MHz..

6 Reserved

Reserved for Future Expansion.

7 Reserved

Reserved for Future Expansion.