82 SA-1110 Developer’s Manual

System Control Module

9.1.2.1 3.6864 MHz Option for GP 27 Alternate Output Function

When GP 27 is configured for its alternate output function by setting bit 27 in both the GAFR and

GPDR, bit 29 of the test unit control register (TUCR) at physical address 0x9003 0008 can be set to

select the 3.6864 MHz oscillator output instead of the 32.768 KHz oscillator output. When

TUCR 29 is cleared the 32.768 KHz oscillator output is selected again. Neither option provides a

fixed phase relationship with any other pin signals; and some glitching may occur when switching

between the two options.

The 3.6864 MHz option is particularly useful for companion chips that require some clock cycles

after assertion of VDD_FAULT or BATT_FAULT. The oscillator output will continue through the

first step of the sleep shutdown sequence, which lasts for one cycle of the power manager’s 32.768

KHz clock (~30 microseconds). Thus, at least 112 cycles of 3.6864 MHz oscillation are provided

prior to shutdown. See Section 9.5.3 for a detailed description of sleep mode and the sleep

shutdown sequence.

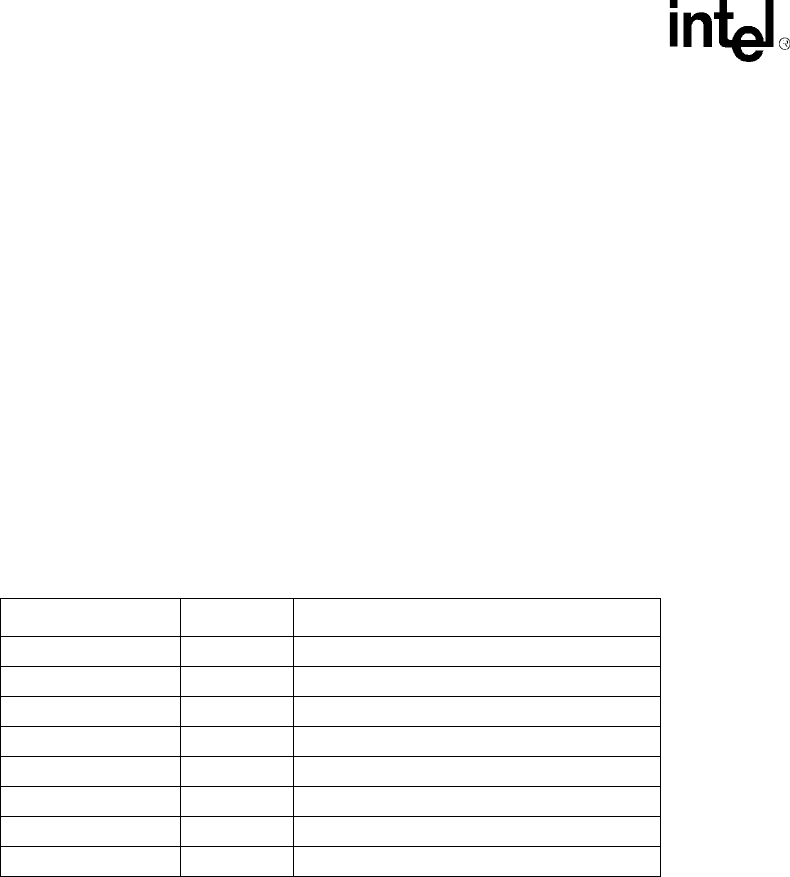

9.1.3 GPIO Register Locations

The following table shows the registers associated with the GPIO block and the physical addresses

used to access them.

Address Name Description

0h 9004 0000 GPLR GPIO pin-level register

0h 9004 0004 GPDR GPIO pin direction register

0h 9004 0008 GPSR GPIO pin output set register

0h 9004 000C GPCR GPIO pin output clear register

0h 9004 0010 GRER GPIO rising-edge detect register

0h 9004 0014 GFER GPIO falling-edge detect register

0h 9004 0018 GEDR GPIO edge detect status register

0h 9004 001C GAFR GPIO alternate function register