376 SA-1110 Developer’s Manual

Peripheral Control Module

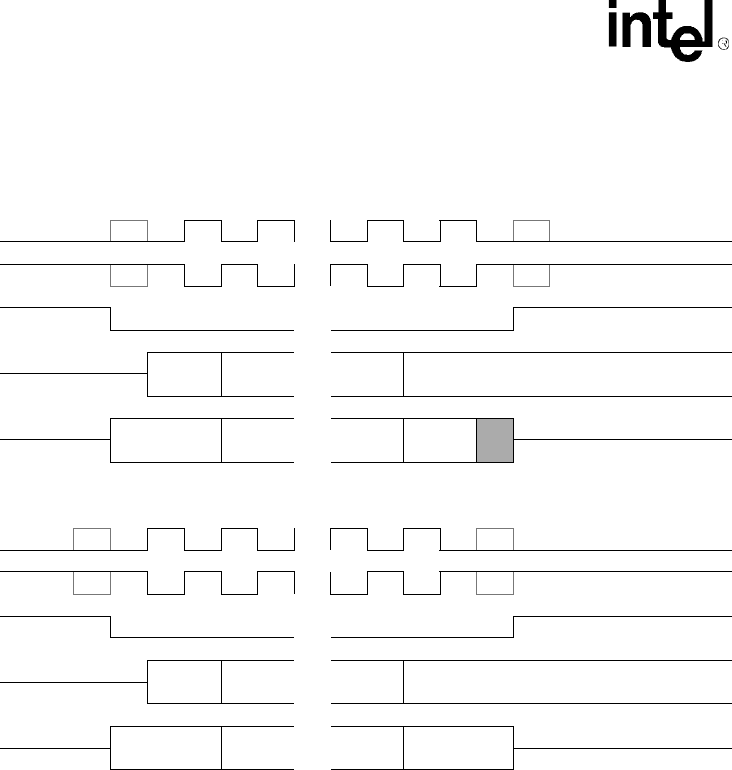

Figure 11-36. Motorola SPI Frame Formats for SPO and SPH Programming

11.12.10.6 External Clock Select (ECS)

The external clock select (ECS) bit selects whether the on-chip 3.6864-MHz clock is used by the

SSP or if an off-chip clock is supplied via GPIO pin 19. When ECS=0, the SSP uses the on-chip

3.6864-MHz clock to produce a range of serial transmission rates ranging from 7.2 Kbps to a

maximum of 1.8432 Mbps. When ECS=1, the SSP uses GPIO 19 to input a clock supplied from

off-chip. The frequency of the off-chip clock can be any value up to 3.6864 MHz. This off-chip

clock is useful when a serial transmission rate, which is not an even multiple of 3.6864 MHz, is

required for synchronization with the target off-chip slave device. When using GPIO pin 19 for the

input clock, the user must also set bit 19 of the GPIO alternate function register (GAFR), and clear

bit 19 of the GPIO pin direction register (GPDR). See the System Control Module chapter.

The following table shows the bit locations corresponding to the three different control bit fields

within SSP control register 1. The reset state of all bits is unknown (indicated by question marks)

and must be initialized before enabling the SSP. Note that writes to reserved bits are ignored and

reads return zero.

SCLK SPO=0

...

SCLK SPO=1

...

SFRM

...

TXD4

Bit N Bit N..

...

Bit 1 Bit 0

RXD4

Bit N Bit N..

...

Bit 1 Bit 0

MSB 4 to 16 Bits LSB

SPH = 0

SCLK SPO=0

...

SCLK SPO=1

...

SFRM

...

TXD4

Bit N Bit N..

...

Bit 1 Bit 0

RXD4

Bit N Bit N..

...

Bit 1 Bit 0

MSB 4 to 16 Bits LSB

SPH = 1