32 SA-1110 Developer’s Manual

Functional Description

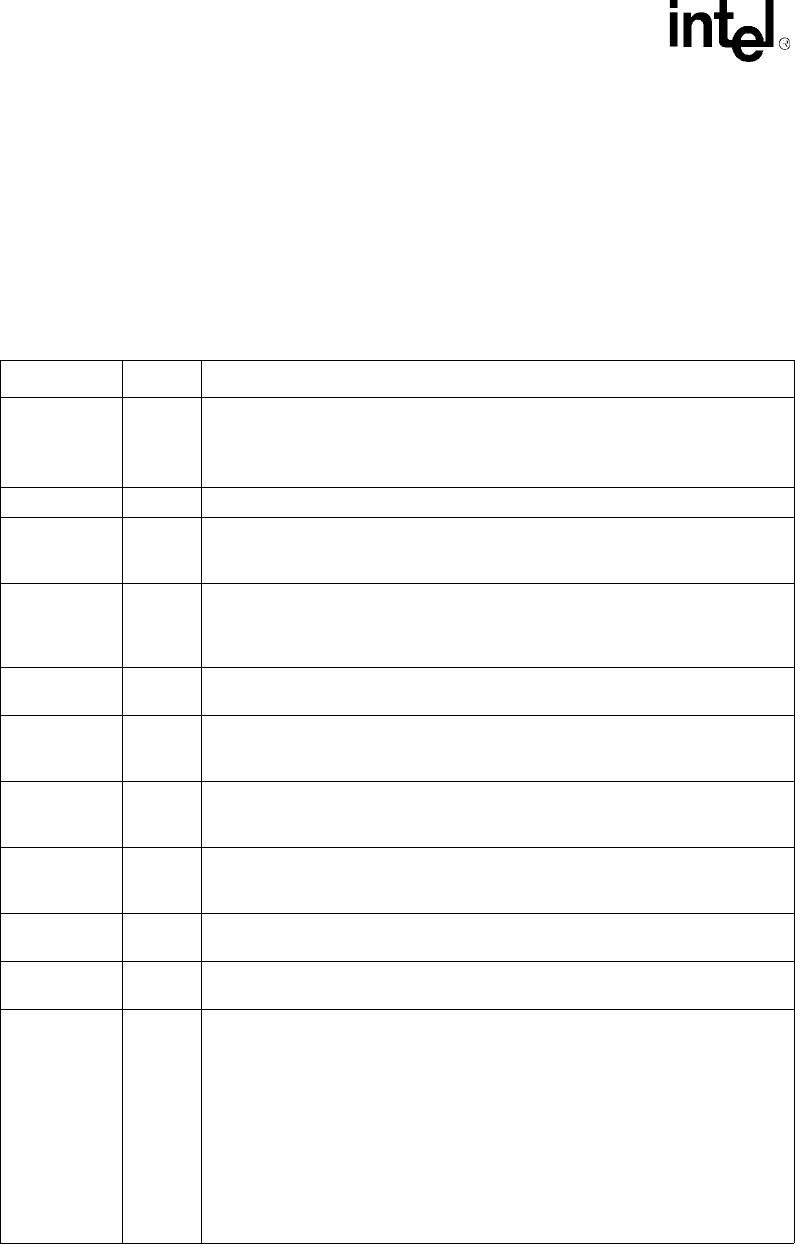

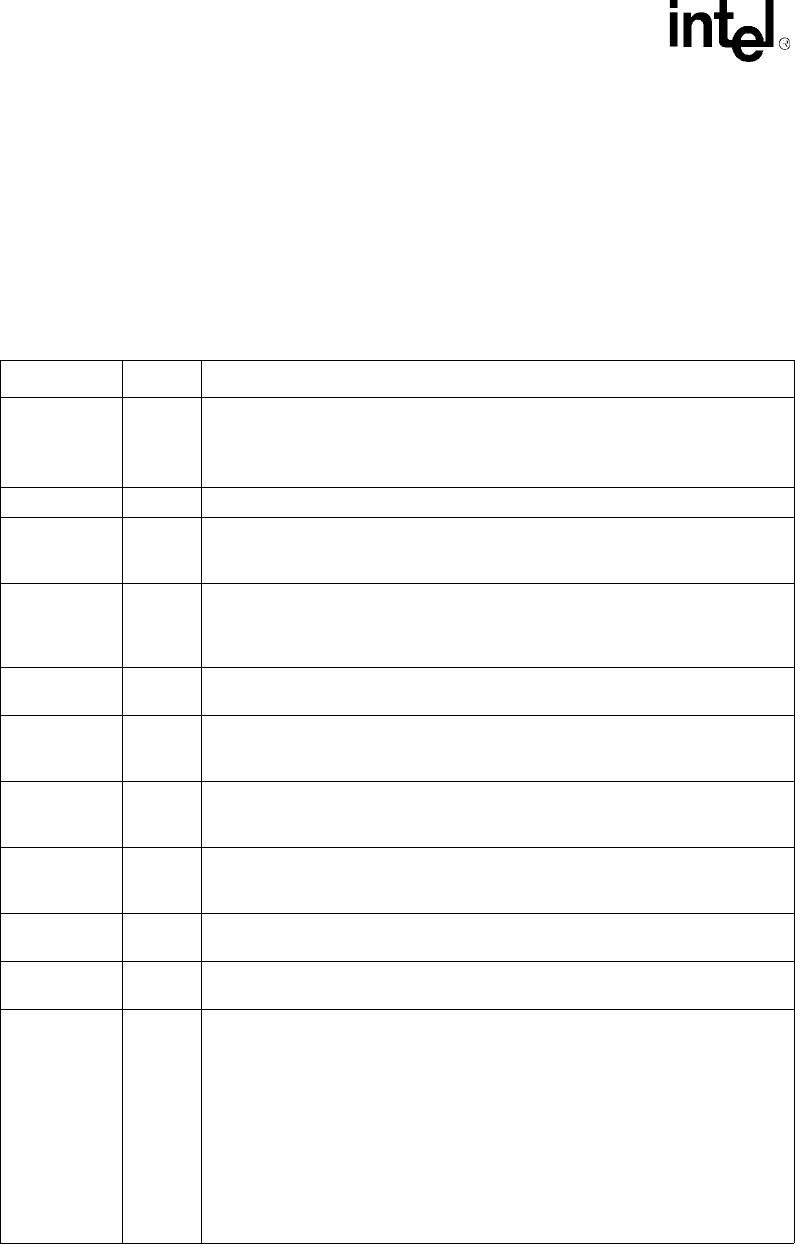

2.3 Signal Description

The following table describes the signals.

KeytoSignalTypes: n– Active low signal

IC – Input, CMOS threshold

ICOCZ – Input, CMOS threshold, output CMOS levels, tristatable

OCZ – Output, CMOS levels, tristatable

Table 2-1. Signal Descriptions (Sheet 1 of 4)

Name Type Description

A[25:0] OCZ Memory address bus. This bus signals the address requested for memory

accesses.

Bits 24..10 carry the 15-bit DRAM address. The static memory devices and the

expansion bus receive address bits 25..0.

D[31:0] ICOCZ Memory data bus. Bits 15..0 are used for 16-bit data busses.

nCS[5:0] OCZ Static chip selects. These signals are chip selects to static memory devices such

as ROM and Flash. They are individually programmable in the memory

configuration registers. Bits 5..3 can be used with variable latency I/O devices.

RDY IC Static data ready signal for nCS[5:3]. This signal should be connected to the data

ready output pins of variable latency I/O devices that require variable data

latencies. Devices selected by nCS[5:3] can share the RDY pin if they drive it high

prior to tristating and a weak external pull-up is present.

nOE OCZ Memory output enable. This signal should be connected to the output enables of

memory devices to control their data bus drivers.

nWE OCZ Memory write enable. This signal should be connected to the write enables of

memory devices.This signal is used in conjunction with nCAS[3:0] to perform byte

writes.

nRAS[3:0]/

nSDCS[3:0]

OCZ DRAM RAS or SDRAM CS for banks 0 through 3. These signals should be

connected to the row address strobe (RAS) pins for asynchronous DRAM or the

chip select (CS) pins for SDRAM.

nCAS[3:0]/

DQM[3:0]

OCZ DRAM CAS or SDRAM DQM for data banks 0 through 3. These signals should be

connected to the column address strobe (CAS) pins for asynchronous DRAM or

the data output mask enables (DQM) for SDRAM.

nSDRAS OCZ SDRAM RAS. This signal should be connected to the row address strobe (RAS)

pins for all banks of SDRAM.

nSDCAS OCZ SDRAM CAS. This signal should be connected to the column address strobe

(CAS) pins for all banks of SDRAM.

SDCKE[1:0] OCZ SDRAM and/or SMROM clock enables.

SDCKE 0 should be connected to the clock enable (CKE) pins of SMROM.

SDCKE 0 is asserted upon any rest (including sleep-exit) if static memory

bank 0 (boot space) is configured for synchronous mask ROM (SMROM_EN = 1);

otherwise it is deasserted upon reset.

SDCKE 1 should be connected to the clock enable pins of SDRAM.They are

deasserted (held low) during sleep. SDCKE 1 always is deasserted upon reset.

The memory controller provides control register bits for deassertion of each

SDCKE pin. However, SDCKE 0 cannot be deasserted via program if

SMROM_EN =1.